# PE9763 EVALUATION KIT USER'S MANUAL

6175 Nancy Ridge Drive, San Diego, CA 92121 (858) 455-0660, Fax (858) 455-0770 http://www.peregrine-semi.com

# **Table of Contents**

| Introduction                                                   |   | 4  |

|----------------------------------------------------------------|---|----|

| Introduction                                                   |   | 5  |

| FCC Labeling RequirementEvaluation Kit Contents & Requirements |   | 5  |

| Evaluation Nit Contents & Nequilements                         |   | U  |

| Software Section                                               |   | 7  |

| Software Installation Instructions                             |   | 8  |

| Software Operation Instructions                                |   | 8  |

| Hardware Section                                               | 1 | 11 |

| Evaluation Kit Configuration                                   |   | 12 |

| Interface Cable Configuration                                  |   | 14 |

| Evaluation Kit Setup for Serial Mode Interface                 |   | 15 |

| Programming Tip                                                |   | 16 |

| Evaluation Kit Setup for Direct Mode Interface                 |   | 16 |

© Copyright 2003 Peregrine Semiconductor Corp. All rights reserved. Printed in the United States of America. No part of this publication may be reproduced, photocopied, stored in a retrieval system, or transmitted by electronic, mechanical or any other means without prior written permission of Peregrine Semiconductor Corp.

Peregrine Semiconductor Corp., the Peregrine logotype, and UTSi are registered trademarks of Peregrine Semiconductor Corp. PE9763 is a trademark of Peregrine Semiconductor Corp.

Peregrine Semiconductor Corp. reserves the right to make improvements to the hardware, firmware or software described in this manual at any time and without notice. While the accompanying material has been carefully reviewed to insure the most accurate information possible, the data are not warranted for absolute accuracy or completeness and are subject to change without notification.

#### Peregrine Semiconductor Corp. Life Support Policy

Peregrine Semiconductor Corp. products are not intended for use in life-critical situations, or as critical components in life-support devices or systems.

Life-support devices or systems are defined as devices or systems that are intended for surgical implant into the body, or that support or sustain life, and whose failure to perform when used in accordance with the instructions provided by the manufacturer, might result in injury to the user.

#### **FCC Compliance Statement**

This device is intended for use only in a research and development environment. It has not been tested for compliance with FCC regulations regarding interference with radio frequency energy. It might cause harmful interference with radio communications. The user assumes responsibility for any interference caused by this device.

# Introduction

#### Introduction

This Evaluation Kit is specifically designed for evaluating the PE9763 3.2 GHz Delta-Sigma modulated (DSM) Fractional-N PLL. The Evaluation Kit allows maximum flexibility for optimizing phase noise, spur, lock time and power performance for specific applications. Using the hardware and software provided in the Evaluation Kit, both serial and direct modes of interface can be demonstrated.

# **Applications Support**

If you have a problem with your evaluation kit, software, or if you have applications questions call **(858) 455-0660** and ask for applications support.

You may also contact us by fax or e-mail:

Fax: **(858) 455-0770**

E-Mail: help@peregrine-semi.com

# FCC Labeling Requirement

This device complies with Part 15 of the FCC Rules. Operation is subject to the following two conditions: (1) this device may cause harmful interference, and (2) this device must accept any interference received including interference that may cause undesired operation.

## **Evaluation Kit Contents & Requirements**

The Evaluation Kit includes all of the specific software and hardware required to evaluate the PE9763. Included in the Evaluation Kit are:

- 1 PE9763 Evaluation Board

- 1 PE9763 3.2 GHz DSM Fractional-N PLL

- 1 Peregrine CD-ROM with application software included

- 2 Jumper shunts

- 1 25-Wire Interface Cable

- 2 2-Wire Power Supply Cables

- 1 4-Wire Power Supply Cable

- 1 Set of Evaluation Kit Data Plots

In order to program the part using serial programming mode the evaluation kit software will need to be installed on a computer with the following minimum requirements:

PC Compatible with Windows™ '95/98/2000

Mouse

Parallel Port

HTML Browser to access CD contents

CAUTION: The PE9763-EK circuit contains components that might be damaged by exposure to voltages in excess of the specified voltage, including voltages produced by electrostatic discharges. Handle the board in accordance with procedures for handling static-sensitive components. Avoid applying excessive voltages to the power supply terminals or signal inputs or outputs.

# Software Section

#### Software Installation Instructions

In order to evaluate the PE9763 performance, the Evaluation Software has to be installed in your computer. Follow the steps below to install the software.

- Start Microsoft Windows™ '95/98/2000.

- 2. Insert the Peregrine CD "PE9763 Evaluation Kit" in a computer CD-ROM drive. If your computer has AutoPlay enabled and the splash screen automatically appears, go to Step 3. If the Peregrine splash screen does not automatically appear, utilize Windows Explorer to browse the CD directory and open the file \cd\startup.htm.

- Select "PE9763 PLL Control Software" from the splash screen and choose the option

of "Run this program from its current location." Identify the desired directory for

installation and select the Unzip option when the WinZip Self-Extractor window

appears.

- 4. Utilize Explorer to run "Setup.exe" from your hard disk directory and follow the instructions on the screen. This will install the Peregrine PE9763 PLL Control Software in the selected directory and add a shortcut to the Windows Start/Programs menu called PE9763 Control.

## Software Operation Instructions

#### Normal Operation

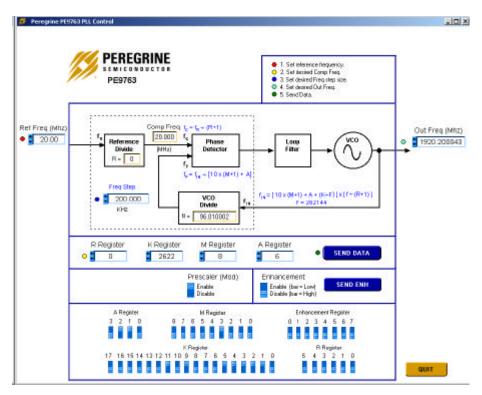

Once the PE9763 control software is installed and launched, a control screen similar to Figure 1 will appear on the screen. To run the PE9763 using your computer's printer port follow the instructions on the screen as shown on the top-right corner for programming. These instructions are described in detail in the following steps for operation parameter of reference frequency 20 MHz, desired comparison frequency 20 MHz, step frequency 200 kHz and VCO out frequency 1920.200 MHz.

- Step 1: Enter reference frequency (fr, crystal frequency) value in MHz into the Ref Freq box (marked by red dot at left). It shows Ref Freq = 20 MHz in Fig. 1.

- Step 2: Set desired comparison frequency (fc) by entering appropriate R value into the R Register box in the middle left side (marked by yellow dot at left). Note that R = fr/fc -1. Verify the value shown in Comp Freq box is the same as the desired fc. Note also that the numbers in the orange boxes are computed values and cannot be directly typed in. It shows R = 0 in Fig. 1.

- Step 3: Enter the desired frequency step in kHz into the Freq Step box. It shows frequency step = 200 kHz in Fig. 1.

Figure 1. Example of the PE9763 Control Screen.

- Step 4: Verify that the Prescaler switch is in the default position "Enable" for a normal operation. Switch it to "Disable" position if the prescaler is to be bypassed (disabled). However, the DSM function does not work in this mode. Thus, always leave Prescaler switch is in the default position "Enable". It shows "Enabled" in Fig. 1.

- Step 5: Verify that the Enhancement selection switch is in the default position "Disable" for a normal operation. It shows "Disable" in Fig. 1.

- Set the VCO frequency to the desired value by typing it into the Out Freq box. Once the frequency value is entered into the box, the corresponded K, M and A register values are displayed in the "K Register", "M Register" and "A Register" Boxes, respectively. Note that the value shown in the Out Freq box might not be the exact frequency entered because of fractional property. Optimize the K Register by increasing or decreasing its value by 1 until the value shown in the Out Freq box is the closest value to the desired out frequency. Instead of entering the frequency value into the Out Freq box, the frequency can also be changed by entering K, M and A register values into the respective "K Register", "M Register" and "A Register" boxes directly in the middle section of

the screen as well. The A, M and K Register values shown in the bottom section are the binary values of the respected register for information only and can not be changed directly here. The display of the binary values is very helpful for setting the register bit values in the direct mode interface. Click the "Send Data" button to program PLL. Fig. 1 shows the resultant output frequency = 1920.200043 MHz, K = 2622, M =8 and A = 6 with the input Out Freq = 1920.2 MHz.

Step 9: To exit the program, click the "QUIT" button.

#### **Enhancement Mode Operation**

The Enhancement Register programming can be achieved by clicking "SEND ENH" button with appropriate Enhancement Register bit shown in Fig. 1 at "ON (high)" position. See Table 10 (Page 10) of the PE9763 Datasheet for the enhancement bit function. The Enhancement mode can then be enabled by switching the Enhancement switch in Fig. 1 to "Enable" position plus setting Switch S6 #5 (ENH) on the evaluation board to "OFF" position at the same time because either one of them can disable the Enhancement mode. Note that the Enhancement switch puts the enhancement control line output from the computer to High or Low instantaneously when the switch is switched to "Disable" or "Enable" position, respectively, without clicking SEND ENH or SEND DATA.

The enhancement register bit values are unknown during power up. To avoid enabling the enhancement mode during power up, set the Enhancement switch in Fig. 1 to "Disable" position and/or setting Switch S6 #5 (ENH) on the evaluation board to "ON" position until the enhancement register bit values are programmed to a known state. The Enhancement selection switch is in the default position "Disable" for a normal operation.

# Hardware Section

# **Evaluation Kit Configuration**

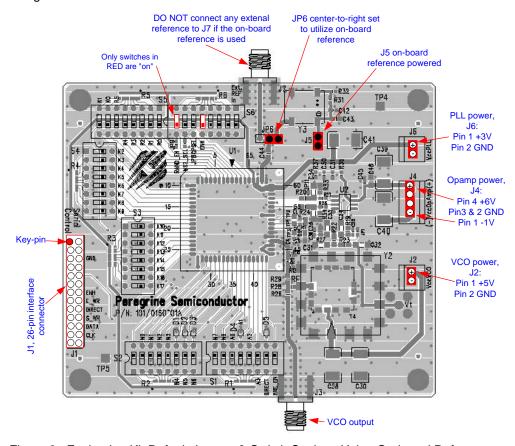

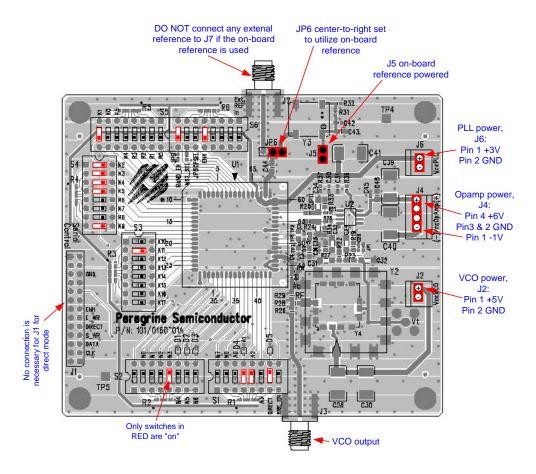

The PE9763 Evaluation Board is configured with an on-board VCO, TCXO reference and a second order active loop filter. The loop filter is followed by 2 low pass filters to filter out high frequency noise. The VCO tuning range is from 1865 MHz to 2055 MHz and the reference oscillator runs at 20 MHz. The active loop filter is designed for a 20 MHz comparison frequency and a 1920.2 MHz output frequency with unity gain crossover at 60 kHz, phase margin of 70 degrees. The 3 dB bandwidth is approximately 75 kHz. The data provided was measured in this configuration with the default jumper settings shown in Figure 2.

Figure 2. Evaluation Kit Default Jumper & Switch Settings Using On-board Reference.

Two jumper shunts (J5 & JP6) configure the Evaluation Board to operate with either the on-board reference oscillator (TCXO) or an external reference applied to J7. Figure 2 shows the proper configuration for utilizing the on-board TCXO reference. A jumper shunt placed in the middle-to-right connection of JP6 as shown connects the output of the TCXO to the PLL  $f_r$  input, while a jumper shunt placed in J5 provides power to the TCXO. Do not connect any external reference to J7 if the on-board reference is selected.

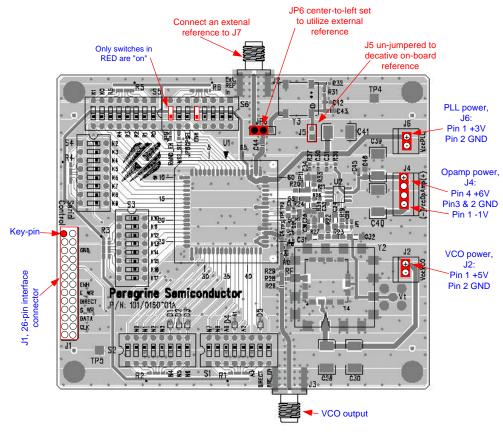

To use an external reference, place the jumper shunt in the middle-to-left connection of JP6 which connects the PLL  $f_r$  input to the J7 SMA connector and remove the jumper shunt on J5 to power-down the TCXO. Figure 3 shows the configuration of using an external reference. The red texts show the necessary modification from Fig. 2.

Figure 3. Jumper Setting to Use an External Reference. The red texts show the necessary modification from Fig. 2.

The PE9763 Evaluation Kit also allows for direct interface using the 37 on-board switches (R0-R5, M0-M8, A0-A3 and K0-K17). Setting the Direct Mode Control switch ON (Switch S1 #7) enables direct mode programming. Setting the Direct Mode Control switch to the OFF position enables serial mode programming allowing for software control.

The default jumper and switch settings are shown in Figure 2, which will place the part into serial programming mode utilizing the on-board reference. Peregrine Semiconductor recommends that the default settings be used initially to bring up the evaluation board and duplicate the enclosed measured data.

# Interface Cable Configuration

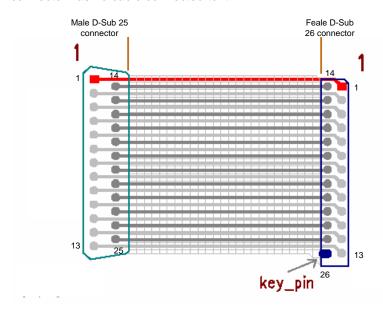

Figure 4 shows the configuration of a 25-wire PSC universal LPT1 interface cable between a male D-sub 25 connector and a female D-sub 26 connector. The naming of pin number is identical for both connectors. The #1 wire of the cable connects the #1 pin of the two connectors, #2 wire for #2 pin, etc. Note that Pin 26 of the female D-sub 26 connector has no cable connected to it.

Figure 4. Configuration of a 25-wire PSC universal LPT1 interface cable between a male D-sub 25 connector and a female D-sub 26 connector.

The individual pin/wire function is described in the following:

#1: NC #6: E\_WR #14: GND

#2: SCLK #7: ENH #15-18: NC

#3: SDATA #8-9: NC #19-25: GND

#4: S\_WR #10-11: GND #26: GND & Key pin

#5: NC #12-13: NC

### Evaluation Kit Setup for Serial Mode Interface

- 1. Verify a jumper shunt is placed on the connector J5 and REF Selector (JP6) is positioned in the middle-to-right connection to select the on-board reference as shown in Fig. 2.

- 2. Verify that Switch S6 #5 (ENH) and S6 #8 (RND\_SEL) are at "ON" position which inhibits enhancement mode and enables K register LSB toggle, respectively. This applies to both the serial and direct interface mode. The rest of the switches should be at "OFF" position.

- 3. Connect power supply cables to the Evaluation Kit board as shown in Fig. 2. Note that the red connector of the power cable is always the positive and the black connector is ground in a 2-wire cable or the negative in a 4-wire cable.

Verify all supplies are turned off prior to connecting to evaluation board.

- Connect the +6/-1 V supply to J4, Pin 4 (+6 V), Pins 3 and 2 (GND), and Pin1 (-1 V)

- 4. Turn on the powers to the board.

- 5. Using the application software provided and described in detail in the previous section, serial programming can be evaluated. To enable software control of the evaluation board, ensure all DIP switches are turned OFF except for ENH (Switch S6 #5) and RND\_SEL (Switch S6 #8) as shown in Figure 2. The 25-wire interface cable should be connected from your computer's printer port to J1 on the evaluation board to enable software control.

- 6. Refer to the previous section for further information on configuring and running the application software. Click the "Send Data" button to program PLL.

- 7. The output of the on-board VCO can be measured by connecting a spectrum analyzer to port J3. Before making modifications to the board, verify and duplicate the performance found in the included plots. Additional GND posts and test points are available on the Evaluation Board for measurement flexibility.

- Note that the Switch S6 #7 (MS2\_SEL) is at "OFF" position. The MS2\_SEL selects MASH 1-1 mode or 1-1-1 mode depending on whether the MS2\_SEL is at "HIGH" or "LOW", respectively. The MASH 1-1 mode is a second order fractional dithering

1

which involves 4 (2<sup>2</sup>) N values (N-1, N, N+1, N+2). On the contrary, the MASH 1-1-1 mode is a third order fractional dithering which involves 8 (2<sup>3</sup>) N values (N-3, N-2... N+3, N+4). After the PLL is in a locked state, the Switch S6 #7 (MS2\_SEL) can be turned on and off to check if the phase noise or spur improves with one of MASH modes.

# **Programming Tip**

When the PLL is first powered on and before programming, the Op Amp output could be resting at a negative voltage preventing proper VCO operation. The PLL will not lock in this condition. If this mode occurs, the power supply for Op Amp (+6/-2 V) should be cycled. To prevent this from happening, the following power on sequence is recommended:

- 1. Turn on power supplies for PLL VDD and VCO VCC.

- 2. Turn on the power supply for the Op Amp.

- 3. Program PLL.

# Evaluation Kit Setup for Direct Mode Interface

Direct mode programming can be evaluated manually without the application software enabled. However, it is handy to have software show the R, K, M and A Registers values in both decimal and binary as shown in Fig. 1. The counters can then be set directly with the on-board switches (S1-S6) according to the binary display of the R, K, M and A Registers values in Fig. 1. To enable direct mode programming, both the ENH (Switch S6 #5) and the Direct (Switch S1 #7) DIP switches should be turned on as shown in Figure 5.

Verify all switches and jumpers are set to as shown in Figure 5. For operation of fr = fc = 20 MHz, Step Freq = 200 kHz and Out Freq = 1920.200 MHz, the switches to be set to "on" include the followings:

S6: #5 for ENH/ and #8 for RAND-FN

S5: #8 for K1

S4: #1 for K2, #2 for K3, #3 for K4, #4 for K5 and #8 for K9

S3: #2 for K11 S2: #5 for M3

S1: #4 for A1, #5 for A2 and #7 for Direct

Other switches including un-marked ones should be left in "OFF" position. The power supplies are the same as those in the serial mode and should be powered on

accordingly. Finally, verify with a spectrum analyzer that the output frequency is 1920.200 MHz.

Figure 5. Jumper & Switch Settings in Direct Mode Interface Using On-board Reference. The settings are for operation parameter of reference frequency 20 MHz, desired comparison frequency 20 MHz, step frequency 200 kHz and VCO out frequency 1920.200 MHz.