# Low Cost Six Channel LED Backlight Driver with Integrated Power Supply

The 34845 series represents high efficiency LED drivers for use in backlighting LCD displays from 10" to 17". Operating from supplies of 5.0 V to 21 V, the 34845 series is capable of driving up to 16 LEDs in series in six separate strings. The LED current tolerance in the six strings is within  $\pm 2\%$  maximum and is set using a resistor to GND.

PWM dimming is performed by applying a PWM input signal to the PWM pin which modulates the LED channels directly. An Enable Pin (EN) provides for low power standby. Alternatively, a single wire scheme selects power down when PWM is connected to the Wake pin and held low.

The integrated boost converter uses dynamic headroom control to automatically set the output voltage. There are three device versions for boost frequency; 34845C is 600 kHz, and the 34845D is 300 kHz. External compensation allows the use of different inductor/ capacitor combinations.

The 34845 includes fault protection modes for LED short and open, overtemperature, overcurrent and overvoltage errors. It features an internally fixed OVP value of 60 V (typical) which protects the device in the event of a failure in the externally programmed OVP. The OVP level can be set by using an external resistor divider. This device is powered using SMARTMOS technology.

#### **Features**

- Input voltage of 5.0 V to 21 V

- Boost output voltage up to 60 V

- · 2.0 A integrated boost FET

- Fixed boost frequency 300 kHz or 600 kHz

- · OTP, OCP, UVLO fault detection

- · LED short/open protection

- Programmable LED current between 3.0 mA and 30 mA

Document Number: MC34845

Rev. 8.0, 5/2015

#### **Applications**

- · PC notebooks

- Netbooks

- GPS screens

- Portable DVD players

- Picture frames

- Smaller screen televisions

- Industrial/instrumentation displays

- · Health care device displays

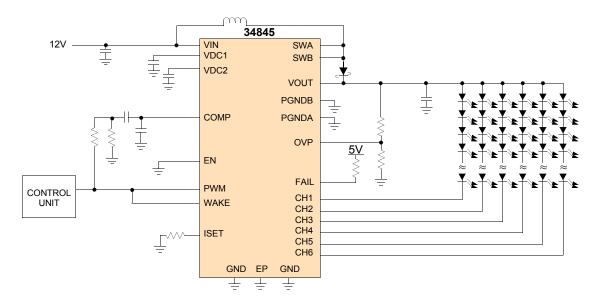

Figure 1. 34845 Simplified Application Diagram

## 1 Orderable Parts

**Table 1. Device Variations**

| Part Number <sup>(1)</sup> | Temperature (T <sub>A</sub> ) | Package    | Boost Switch Current Limit I <sub>BOOST_LIMIT</sub> (A) |      | Switc | hing Frequency<br>f <sub>S</sub> (kHz) |     | Slope Co | mpensatio<br>(V/μs) | n V <sub>SLOPE</sub> |     |

|----------------------------|-------------------------------|------------|---------------------------------------------------------|------|-------|----------------------------------------|-----|----------|---------------------|----------------------|-----|

|                            | ('A)                          |            | Min                                                     | Тур  | Max   | Min                                    | Тур | Max      | Min                 | Тур                  | Max |

| MC34845CEP                 | -40 to 85 °C                  | 24 QFN-EP  | 1.9                                                     | 2.1  | 2.3   | 540                                    | 600 | 660      | _                   | 0.52                 | _   |

| MC34845DEP                 |                               | 27 XI N-LI | 2.1                                                     | 2.35 | 2.6   | 270                                    | 300 | 330      |                     | 0.22                 | 1   |

<sup>1.</sup> To order parts in Tape and Reel, add the R2 suffix to the part number.

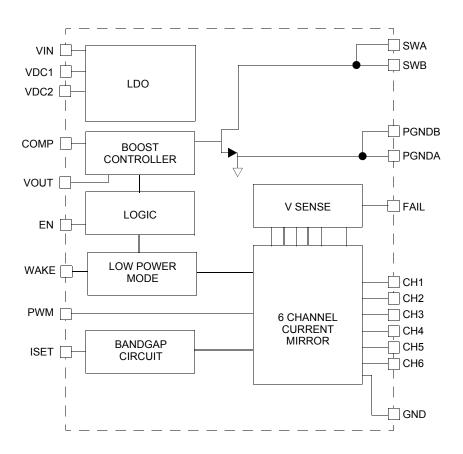

# 2 Internal Block Diagram

Figure 2. 34845 Simplified Internal Block Diagram

## 3 Pin Connections

## 3.1 Pinout Diagram

TRANSPARENT TOP VIEW 20 19 VIN 1 (18 WAKE PGNDB 2 (17 COMP SWB 3 16 PWM EP GND 15 ISET SWA 4 PGNDA 14 FAIL EN 6 (13 GND 12

Figure 3. 34845 Pin Connections

## 3.2 Pin Definitions

Table 2. 34845 Pin Definitions

| Pin Number | Pin Name  | Definition                                                                                                                                                                                                 |

|------------|-----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1          | VIN       | Main voltage supply Input. IC Power input supply voltage, is used internally to produce internal voltage regulation for logic functioning, and also as an input voltage for the boost regulator.           |

| 2          | PGNDB     | Power ground. This is the ground pin for the internal Boost FET.                                                                                                                                           |

| 3          | SWB       | Boost switch node connection B. Switching node of boost converter.                                                                                                                                         |

| 4          | SWA       | Boost switch node connection A. Switching node of boost converter.                                                                                                                                         |

| 5          | PGNDA     | Power ground. This is the ground pin for the internal Boost FET.                                                                                                                                           |

| 6          | EN        | Enable pin (active high, internal pull-down).                                                                                                                                                              |

| 7 - 12     | CH1 - CH6 | LED string connections 1 to 6. LED current drivers. Each line has the capability of driving up to 30 mA.                                                                                                   |

| 13, 19, 21 | GND       | Ground Reference for all internal circuits other than the Boost FET. The Exposed Pad (EP) should be used for thermal heat dissipation.                                                                     |

| 14         | FAIL      | Fault detected pin (open drain):  • No Failure = Low-impedance pull-down  • Failure = High-impedance  When a fault situation is detected, this pin goes into high-impedance.                               |

| 15         | ISET      | LED current setting. The maximum current is set using a resistor from this pin to GND.                                                                                                                     |

| 16         | PWM       | External PWM control signal.                                                                                                                                                                               |

| 17         | COMP      | Boost compensation component connection. This passive pin is used to compensate the boost converter. Add a capacitor and a resistor in series to GND to stabilize the system as well as a shunt capacitor. |

| 18         | WAKE      | Low power consumption mode for single wire control. This is achieved by connecting the WAKE and PWM pins together and grounding the ENABLE (EN) pin.                                                       |

| 20         | VDC1      | 2.5 V internal voltage decoupling. This pin is for internal use only, and not to be used for other purposes. A capacitor of 2.2 $\mu$ F should be connected between this pin and ground.                   |

| 22         | OVP       | External boost overvoltage setting. Requires a resistor divider from VOUT to GND. If no external OVP setting is desired, this pin should be grounded.                                                      |

#### Table 2. 34845 Pin Definitions (continued)

| Pin Number | Pin Name | Definition                                                                                                                                                                                 |

|------------|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 23         | VDC2     | $6.0~V$ internal voltage decoupling. This pin is for internal use only, and not to be used for other purposes. A capacitor of $2.2~\mu F$ should be connected between this pin and ground. |

| 24         | VOUT     | Boost voltage output feedback.                                                                                                                                                             |

| EP         | EP       | Ground and thermal enhancement pad                                                                                                                                                         |

## 4 Electrical Characteristics

## 4.1 Absolute Maximum Ratings

#### **Table 3. Absolute Maximum Ratings**

All voltages are with respect to ground unless otherwise noted. Exceeding these ratings may cause a malfunction or permanent damage to the device.

| Symbol               | Ratings                                                                                                                                                                            | Value                                                                                                             | Unit | Notes    |

|----------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------|------|----------|

| ELECTRICAL RA        | ATINGS                                                                                                                                                                             | 1                                                                                                                 |      |          |

| $V_{MAX}$            | Maximum Pin Voltages  • SWA, SWB, VOUT  • CH1, CH2, CH3, CH4, CH5, CH6 (Off state)  • CH1, CH2, CH3, CH4, CH5, CH6 (On state)  • FAIL  • OVP  • COMP, ISET  • PWM, WAKE  • EN, VIN | -0.3 to 65<br>-0.3 to 45<br>-0.3 to 20<br>-0.3 to 7.0<br>-0.3 to 7.75<br>-0.3 to 2.7<br>-0.3 to 5.5<br>-0.3 to 24 | V    |          |

| I <sub>LED_MAX</sub> | Maximum LED Current per Channel                                                                                                                                                    | 33                                                                                                                | mA   |          |

| V <sub>ESD</sub>     | ESD Voltage<br>Human Body Model (HBM)<br>Machine Model (MM)                                                                                                                        | ±2000<br>±200                                                                                                     | V    | (2)      |

| THERMAL RATI         | NGS                                                                                                                                                                                |                                                                                                                   | •    | •        |

| T <sub>A</sub>       | Operating Ambient Temperature Range                                                                                                                                                | -40 to 85                                                                                                         | °C   |          |

| T <sub>J</sub>       | Maximum Junction Temperature                                                                                                                                                       | 150                                                                                                               | °C   |          |

| TS                   | Storage Temperature Range                                                                                                                                                          | -40 to 150                                                                                                        | °C   |          |

| T <sub>PPRT</sub>    | Peak Package Reflow Temperature During Reflow                                                                                                                                      | Note 4                                                                                                            | °C   | (3), (4) |

| $T_{\thetaJA}$       | Thermal Resistance Junction to Ambient                                                                                                                                             | 36                                                                                                                | °C/W | (5)      |

| $T_{	hetaJC}$        | Thermal Resistance Junction to Case                                                                                                                                                | 3.1                                                                                                               | °C/W | (6)      |

| $P_{D}$              | Power Dissipation  • T <sub>A</sub> = 25 °C  • T <sub>A</sub> = 85 °C                                                                                                              | 3.4<br>1.8                                                                                                        | w    | (5)      |

- 2. ESD testing is performed in accordance with the Human Body Model (HBM) (AEC-Q100-2) ( $C_{ZAP}$  = 100 pF,  $R_{ZAP}$  = 1500  $\Omega$ ), and the Machine Model (MM) ( $C_{ZAP}$  = 200 pF,  $R_{ZAP}$  = 0  $\Omega$ ).

- 3. Pin soldering temperature limit is for 10 seconds maximum duration. Not designed for immersion soldering. Exceeding these limits may cause malfunction or permanent damage to the device.

- 4. Freescale's Package Reflow capability meets Pb-free requirements for JEDEC standard J-STD-020C. For Peak Package Reflow Temperature and Moisture Sensitivity Levels (MSL), Go to www.freescale.com, search by part number [e.g. remove prefixes/suffixes and enter the core ID to view all orderable parts. (i.e. MC33xxxD enter 33xxx), and review parametrics.

- Per JEDEC51-8 Standard for Multilayer PCB.

- 6. Theoretical thermal resistance is from the die junction to the exposed pad.

## 4.2 Static and Dynamic Electrical Characteristics

#### Table 4. Static and Dynamic Electrical Characteristics

Characteristics noted under conditions  $V_{IN}$  = 12 V,  $V_{OUT}$  = 35 V,  $I_{LED}$  = 30 mA,  $f_S$  = 600 kHz,  $f_{PWM}$  = 600 Hz - 40 °C  $\leq$   $T_A \leq$  85 °C, unless otherwise noted. Typical values noted reflect the approximate parameter means at  $T_A$  = 25 °C under nominal conditions, unless otherwise noted.

| Symbol                                 | Characteristic                                                                                                   | Min        | Тур         | Max        | Unit | Notes |

|----------------------------------------|------------------------------------------------------------------------------------------------------------------|------------|-------------|------------|------|-------|

| SUPPLY                                 | •                                                                                                                |            |             |            | •    |       |

| V <sub>IN</sub>                        | Supply Voltage                                                                                                   | 5.0        | 10          | 21         | V    |       |

| I <sub>SHUTDOWN</sub>                  | Supply Current when in Shutdown Mode • EN = Low, PWM = Low                                                       | -          | 2.0         | 10         | μА   |       |

| I <sub>OPERATIONAL</sub>               | Supply Current when Operational Mode  • Boost = Pulse Skipping, Channels = 1% of Duty Cycle EN = High, PWM = Low | -          | 5.0         | 6.5        | mA   |       |

| UVLO                                   | Undervoltage Lockout  • V <sub>IN</sub> Rising                                                                   | 4.0        | -           | 4.4        | V    |       |

| UVLO <sub>HYST</sub>                   | Undervoltage Hysteresis  • V <sub>IN</sub> Falling                                                               | -          | 0.25        | -          | V    |       |

| V <sub>DC1</sub>                       | VDC1 Voltage • C <sub>VDC1</sub> = 2.2 μF                                                                        | 2.4        | 2.5         | 2.6        | V    | (7)   |

| V <sub>DC2</sub>                       | VDC2 Voltage (V <sub>IN</sub> between 7.0 V and 21 V) • C <sub>VD2C</sub> = 2.2 μF                               | 5.7        | 6.0         | 6.3        | V    | (7)   |

| вооѕт                                  | 1                                                                                                                | 1          |             |            |      | · I   |

| V <sub>OUT1</sub><br>V <sub>OUT2</sub> | Output Voltage Range  • VIN = 5.0 V  • VIN = 21 V                                                                | 8.0<br>24  |             | 43<br>60   | V    | (8)   |

| I <sub>BOOST_LIMIT</sub>               | Boost Switch Current Limit • 34845C • 34845D                                                                     | 1.9<br>2.1 | 2.1<br>2.35 | 2.3<br>2.6 | А    |       |

| t <sub>BOOST_TIME</sub>                | Boost Switch Current Limit Timeout                                                                               | -          | 10          | -          | ms   |       |

| R <sub>DS(on)</sub>                    | RDSON of Internal FET  • I <sub>DRAIN</sub> = 1.0 A                                                              | -          | 300         | 520        | mW   |       |

| I <sub>BOOST_LEAK</sub>                | Boost Switch Off State Leakage Current  • V <sub>SWA,SWB</sub> = 60 V                                            | -          | -           | 1.0        | mA   |       |

| VOUT <sub>LEAK</sub>                   | Feedback pin Off State Leakage Current  • V <sub>OUT</sub> = 60 V                                                | -          | -           | 500        | mA   |       |

| EFF <sub>BOOST</sub>                   | Peak Boost Efficiency • $V_{OUT}$ = 33 V, RL = 330 $\Omega$                                                      | -          | 90          | -          | %    | (9)   |

| I <sub>LED</sub> /V <sub>IN</sub>      | Line Regulation • V <sub>IN</sub> = 7.0 V to 21 V, I <sub>CH</sub> = 30 mA                                       | -0.2       | -           | 0.2        | %/V  |       |

| I <sub>LED</sub> /V <sub>LED</sub>     | Load Regulation  • V <sub>LED</sub> = 24 V to 40 V (all Channels), I <sub>CH</sub> = 30 mA                       | -0.2       | -           | 0.2        | %/V  |       |

| D <sub>MIN</sub>                       | Minimum Duty Cycle                                                                                               | -          | 10          | 15         | %    |       |

| D <sub>MAX</sub>                       | Maximum Duty Cycle                                                                                               | 88         | 90          | -          | %    |       |

| V <sub>OVP_INT</sub>                   | OVP Internally Fixed Value • (no external voltage resistor divider)                                              | 56         | 60          | 64         | V    |       |

- 7. This output is for internal use only and not to be used for other purposes.

- 8. Minimum and maximum output voltages are dependent on Min/Max duty cycle condition.

- 9. Boost efficiency test is performed under the following conditions:  $f_{SW}$  = 600 kHz,  $V_{IN}$  = 12 V,  $V_{OUT}$  = 33 V and  $R_L$  = 330  $\Omega$ . The following external components are used: L = 10  $\mu$ H, DCR = 0.1  $\Omega$ ,  $C_{OUT}$  = 3x1  $\mu$ F (ceramic), Schottky diode  $V_F$  = 0.35 V.

#### Table 4. Static and Dynamic Electrical Characteristics (continued)

Characteristics noted under conditions  $V_{IN}$  = 12 V,  $V_{OUT}$  = 35 V,  $I_{LED}$  = 30 mA,  $f_S$  = 600 kHz,  $f_{PWM}$  = 600 Hz - 40 °C  $\leq$   $T_A \leq$  85 °C, unless otherwise noted. Typical values noted reflect the approximate parameter means at  $T_A$  = 25 °C under nominal conditions, unless otherwise noted.

| Symbol                         | Characteristic                                                                                                                       | Min          | Тур          | Max          | Unit | Notes |

|--------------------------------|--------------------------------------------------------------------------------------------------------------------------------------|--------------|--------------|--------------|------|-------|

| BOOST (CONTINU                 | JED)                                                                                                                                 | <b>-</b>     | •            | •            | •    |       |

| V <sub>OVP_EXT</sub>           | OVP Programming Range • (set through an external resistor divider)                                                                   | 15           | -            | 60           | V    | (10)  |

| V <sub>REF_OVP</sub>           | OVP Reference Voltage                                                                                                                | 6.3          | 6.9          | 7.5          | V    |       |

| I <sub>SINK_OVP</sub>          | OVP Sink Current                                                                                                                     | -            | 0.2          | -            | μА   |       |

| f <sub>S</sub>                 | Switching Frequency • 34845C • 34845D                                                                                                | 540<br>270   | 600<br>300   | 660<br>330   | kHz  |       |

| t <sub>SS</sub>                | Soft Start Time (f <sub>s</sub> = 600 kHz, 100% PWM duty)                                                                            | -            | 3.0          | -            | ms   |       |

| SS_ <sub>VOUT</sub>            | Soft Start V <sub>OUT</sub> Overshoot (f <sub>s</sub> = 600 kHz, 100% PWM duty)                                                      | -            | -            | OVP          | V    |       |

| BOOST_t <sub>R</sub>           | Boost Switch Rise Time                                                                                                               | -            | 8.0          | -            | ns   |       |

| BOOST_t <sub>F</sub>           | Boost Switch Fall Time                                                                                                               | -            | 6.0          | -            | ns   |       |

| A <sub>CSA</sub>               | Current sense Amplifier Gain                                                                                                         | -            | 9.0          | -            |      |       |

| $G_M$                          | OTA Transconductance                                                                                                                 | -            | 200          | -            | μS   |       |

| I <sub>SS</sub>                | Transconductance Sink and Source Current Capability                                                                                  | -            | 100          | -            | μА   |       |

| $V_{SLOPE}$                    | Slope Compensation • 34845C • 34845D                                                                                                 |              | 0.52<br>0.22 | -<br>-       | V/µs |       |

| ED DRIVER                      |                                                                                                                                      | •            |              |              | •    |       |

| I <sub>LED</sub>               | LED Driver Sink Current • R <sub>ISET</sub> = 51 k $\Omega$ 0.1%, PWM = 3.3 V • R <sub>ISET</sub> = 5.1 k $\Omega$ 0.1%, PWM = 3.3 V | 2.88<br>29.4 | 3.0<br>30    | 3.12<br>30.6 | mA   |       |

| V <sub>ISET</sub>              | ISET Pin Voltage • R <sub>ISET</sub> = 5.1 kΩ 0.1%                                                                                   | 2.011        | 2.043        | 2.074        | V    |       |

| V <sub>MIN</sub>               | Regulated Minimum Voltage Across LED Drivers • Pulse Width > 400 ns                                                                  | 0.675        | 0.75         | 0.825        | V    |       |

| I <sub>TOLERANCE</sub>         | LED Current Channel to Channel Tolerance  • 10 mA ≤ l <sub>LED</sub> ≤ 30 mA  • 3.0 mA ≤ l <sub>LED</sub> < 10 mA                    | -2.0<br>-4.0 |              | 2.0<br>4.0   | %    |       |

| I <sub>CH_LEAK</sub>           | Off State leakage Current, All Channels  • V <sub>CH</sub> = 45 V                                                                    | -            | -            | 1.0          | μА   |       |

| t <sub>R</sub> /t <sub>F</sub> | LED Channels Rise and Fall Time                                                                                                      | -            | 50           | 75           | ns   |       |

| O <sub>FDV</sub>               | LED Open Protection, Channel Disabled if V <sub>CH</sub> ≤ O <sub>FDV</sub>                                                          | -            | -            | 0.55         | V    | 1     |

| S <sub>FDV</sub>               | LED Short Protection Voltage, Channel Disabled if $V_{CH} \ge S_{FDV}$ (channel on time $\ge 10~\mu s$ )                             | 6.5          | 7.0          | 7.5          | V    |       |

| AIL PIN                        |                                                                                                                                      |              |              |              |      | -1    |

| I <sub>FAIL_LEAK</sub>         | Off State Leakage Current  • V <sub>FAIL</sub> = 5.5 V                                                                               | -            | -            | 5.0          | μА   |       |

| V <sub>OL</sub>                | On State Voltage Drop • I <sub>SINK</sub> = 4.0 mA                                                                                   | -            | -            | 0.4          | V    |       |

| OVERTEMPERAT                   | URE SHUTDOWN                                                                                                                         | 1            | 1            | 1            | 1    |       |

| OTT <sub>SHUTDOWN</sub>        | Over-temperature Threshold (shutdown mode) • Rising • Hysteresis                                                                     | 150          | 165<br>25    |              | °C   |       |

| Notes                          | I.                                                                                                                                   | 1            | I            | I            | 1    | _1    |

<sup>10.</sup> The OVP level must be set 5.0 V above the worst-case LED string voltage.

#### Table 4. Static and Dynamic Electrical Characteristics (continued)

Characteristics noted under conditions  $V_{IN}$  = 12 V,  $V_{OUT}$  = 35 V,  $I_{LED}$  = 30 mA,  $f_S$  = 600 kHz,  $f_{PWM}$  = 600 Hz - 40 °C  $\leq$   $T_A \leq$  85 °C, unless otherwise noted. Typical values noted reflect the approximate parameter means at  $T_A$  = 25 °C under nominal conditions, unless otherwise noted

| Symbol                 | Characteristic                                                      | Min  | Тур | Max  | Unit | Notes |

|------------------------|---------------------------------------------------------------------|------|-----|------|------|-------|

| PWM INPUT              |                                                                     | 1    |     |      | l .  |       |

|                        | PWM Dimming Mode LED Current Control                                |      |     |      |      |       |

| DIA/A                  | <ul> <li>PWM = 3.3 V, f<sub>PWM</sub> = 600 Hz 10% duty;</li> </ul> | 9.9  | 10  | 10.1 | 0/   |       |

| PWM <sub>CONTROL</sub> | • PWM = 3.3 V, f <sub>PWM</sub> = 600 Hz 50% duty                   | 49.5 | 50  | 50.5 | %    |       |

|                        | • PWM = 3.3 V, f <sub>PWM</sub> = 600 Hz 100% duty                  | -    | 100 | -    |      |       |

|                        | Input Minimum Pulse PWM Pin (V <sub>PWM</sub> = 3.3 V)              |      |     |      |      |       |

|                        | Start-up (Wake mode)                                                | 1.6  | -   | -    |      |       |

| t <sub>PWM_IN</sub>    | Operational (Wake mode)                                             | -    | 0.2 | -    | μS   |       |

|                        | Start-up (Enable mode)                                              | 0.4  | -   | -    |      |       |

|                        | operational (Enable mode)                                           | -    | 0.2 | -    |      |       |

| f <sub>PWM</sub>       | Input Frequency Range for PWM Pin                                   | DC   | -   | 100  | kHz  |       |

| WAKE                   |                                                                     | ·    |     |      |      |       |

| t <sub>SHUTDOWN</sub>  | Shutdown Mode Timeout                                               | 27   | 30  | 33   | ms   |       |

| LOGIC INPUTS (F        | PWM)                                                                |      |     |      |      |       |

| $V_{ILL}$              | Input Low Voltage                                                   | -0.3 | -   | 0.5  | V    |       |

| V <sub>IHL</sub>       | Input High Voltage                                                  | 1.5  | -   | 5.5  | V    |       |

| I <sub>SINK</sub>      | Input Current                                                       | -1.0 | -   | 1.0  | μΑ   |       |

| OGIC INPUTS (E         | EN)                                                                 |      |     |      |      | •     |

| $V_{ILL}$              | Input Low Voltage                                                   | -0.3 | -   | 0.5  | V    |       |

| $V_{IHL}$              | Input High Voltage                                                  | 2.1  | -   | 21   | V    |       |

| I <sub>SINK</sub>      | Input Current (V <sub>EN</sub> = 12 V)                              | -    | 6.0 | 10   | μΑ   |       |

| LOGIC INPUTS (V        | VAKE)                                                               | •    |     | •    |      |       |

| $V_{ILL}$              | Input Low Voltage                                                   | -0.3 | -   | 0.5  | V    |       |

| V <sub>IHL</sub>       | Input High Voltage                                                  | 2.1  | -   | 5.5  | V    |       |

| I <sub>SINK</sub>      | Input Current                                                       | -1.0 | -   | 1.0  | μΑ   |       |

## 5 Functional Description

#### 5.1 Introduction

LED backlighting has been popular for use in small LCD displays for many years. This technology is now rapidly replacing the incumbent Cold Cathode Fluorescent Lamp (CCFL) in mid-size displays such as those used use in notebooks, monitors, and industrial/ consumer displays. LEDs offer a number of advantages compared to the CCFL, including lower power, thinner, longer lifetime, low voltage drive, accurate wide-range dimming control, and advanced architectures for improved image quality. LEDs are also void of hazardous materials such as mercury which is used in CCFL.

LED backlights use different architecture depending on the size of the display and features required. For displays in the 10" to 17" + range such as those used in notebooks, edge-lit backlights offer very thin designs down to 2.0 mm or less. The efficiency of the LED backlight also extends battery life in portable equipment compared to CCFL. In large size panels, direct backlights support advanced architectures such as local dimming, in which power consumption and contrast ratio are drastically improved. Edge lighting can also be used in large displays when low cost is the driving factor.

The 34845 targets mid size panel applications in the 10" to 17" + range with edge-lit backlights. The device supports LED currents up to 30 mA and supports up to six strings of LEDs. This enables backlights up to 10 W to be driven from a single device. The device includes a boost converter to deliver the required LED voltage from either a two or three cell Li-ion battery, or a direct 12 V input supply. The current drivers match the current between devices to provide superior uniformity across the display. The 34845 provides for a wide range of PWM dimming from a direct PWM control input.

#### 5.2 Functional Device Operation

#### 5.2.1 Power Supply

The 34845 supports 5.0 V to 21 V at the VIN input pin. Two internal regulators generate internal rails for internal operation. Both rails are de-coupled using capacitors on the VDC1 and VDC2 pins. The VIN, VDC1, and VDC2 supplies each have their own UVLO mechanisms. When any voltage is below the UVLO threshold, the device stops operating. All UVLO comparators have hysteresis to ensure constant on/off cycling does not occur.

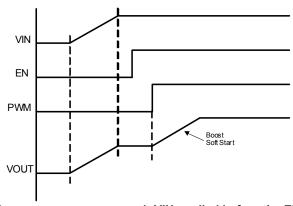

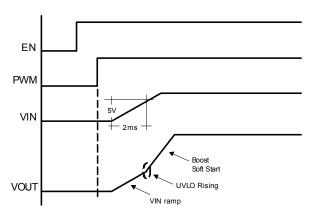

The power up sequence for applying  $V_{IN}$  respect to the ENABLE and PWM signals is important since the 34845 device behaves differently depending on how the sequence of these signals is applied. For the case where VIN is applied before the ENABLE and PWM signals, the device has no limitation in terms of how fast the  $V_{IN}$  ramp should be. However for the case where the PWM and ENABLE signals are applied before  $V_{IN}$ , the ramp up time of  $V_{IN}$  between 0 V and 5.0 V should be no longer than 2.0 ms. Figure 4 and Figure 5 illustrate the two different power up conditions.

Figure 4. Power up sequence case 1, VIN applied before the ENABLE and PWM signals. No limitation for VIN ramp up time.

Figure 5. Power up sequence case 2, VIN applied after the ENABLE and PWM signals. VIN ramp up time between 0 V and 5.0 V should be not higher than 2.0 ms

#### 5.2.2 Boost Converter

The boost converter uses a Dynamic Headroom Control (DHC) loop to automatically set the output voltage needed to drive the LED strings. The DHC is designed to operate under specific pulse width conditions in the LED drivers. It operates for pulse widths higher than 400 ns. If the pulse widths are shorter than specified, the DHC circuit does not operate and the voltage across the LED drivers increase to a value given by the OVP, minus the total LED voltage in the LED string. It is therefore imperative to select the proper OVP level to avoid exceeding the max off state voltage of the LED drivers (45 V).

The boost operates in current mode and is compensated externally through a type 2 network on the COMP pin. A modification of the compensation network is suggested to minimize the amplitude of the ripple at V<sub>OUT</sub>. The details of the suggested compensation network are shown in <u>Figure 10</u> and <u>Figure 11</u>.

An integrated 2.0 A minimum FET supplies the required output current. An overcurrent protection circuit limits the output current cycle-by-cycle to I<sub>OCP</sub>. If the condition exists longer than 10 ms, then the device shuts down. The frequency of the boost converter is internally set to 300 kHz or 600 kHz, depending on the device's version.

The boost also includes a soft start circuit. Each time the IC comes out of shutdown mode, the soft start period lasts for t<sub>SS</sub>.

Overvoltage protection is also included. The device has an internally fixed OVP value of 60 V (typical) which serves as a secondary fault protection mechanism, in the event the externally programmed OVP fails (i.e. resistor divider opens up). While the internal 60 V OVP detector can be used exclusively without the external OVP network, this is only recommended for applications where the LED string voltage approaches 55 V or more. The OVP level can be set by using an external resistor divider connected between the output voltage and ground with its output connected to the OVP pin. The OVP can be set up to 60 V by varying the resistor divider to match the OVP internal reference of 6.9 V (typical).

#### 5.2.3 LED Driver

The six channel LED driver provides current matching for six LED strings to within  $\pm 2\%$  maximum. The current in the strings is set using a resistor tied to GND from the ISET pin. The LED current level is given by the equation:  $R_{SET} = 153/I_{LED}$ . The accuracy of the  $R_{SET}$  resistor should be 0.1% for best performance.

#### 5.2.4 LED Error Detect

If an LED is open, the output voltage ramps to the OVP level. If there is still no current in the LED string, the LED channel is turned off and the output voltage ramps back down to normal operating level.

If LEDs are shorted and the voltage in any of the channels is greater than the SFDV threshold (7.0 V typical), then the device turns off this channel. However if the on-time of the channels is less than 10  $\mu$ s, the SFDV circuit does not disable any of the channels, regardless of the voltage across them. All the LED errors can be cleared by recycling the EN pin or applying a complete power-on-reset (POR).

#### 5.2.5 WAKE Operation

The WAKE pin provides the means to set the device for low power consumption (shutdown mode) without the need of an extra logic signal for enable. This is achieved by connecting the WAKE and PWM pins together, and tying the EN pin to ground. In this configuration, the PWM signal is used to control the LED channels, while allowing low power consumption by setting the device into its shutdown mode every time the PWM signal is kept low for longer time than the WAKE time out of 27 ms.

#### 5.2.6 Overtemperature Shutdown and Temperature Control Circuits

The 34845 includes over-temperature protection. If the internal temperature exceeds the over-temp threshold OTT<sub>SHUTDOWN</sub>, then the device shuts down all functions. Once the temperature falls below the low level threshold, the device is re-enabled.

#### **5.2.7 FAIL Pin**

The FAIL pin is at its low-impedance state when no error is detected. However, if an error such as an LED channel open or boost overcurrent is detected, the FAIL pin goes into high-impedance. Once a failure is detected, the FAIL pin can be cleared by recycling the EN pin or applying a complete power-on-reset (POR). If the detected failure is an Over-current time-out, the EN pin or a POR must be cycled/executed to restart the part.

## 5.3 Typical Performance Curves

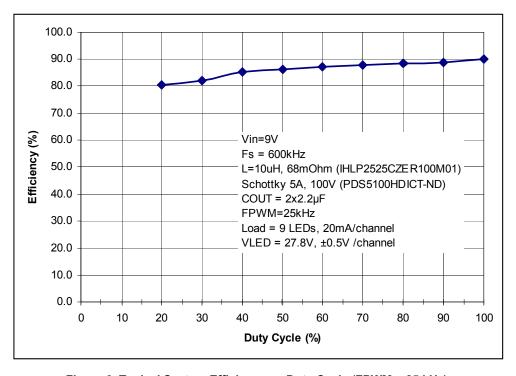

Figure 6. Typical System Efficiency vs Duty Cycle (FPWM = 25 kHz)

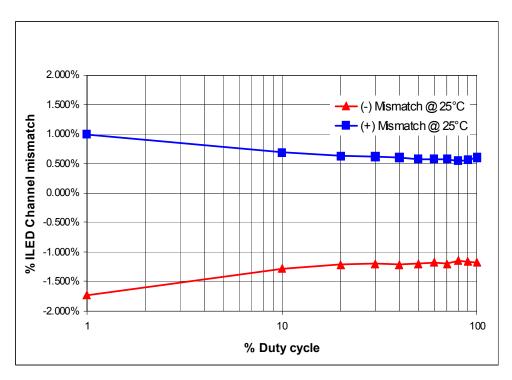

Figure 7. Typical ILED Dimming Linearity (FPWM = 25 kHz)

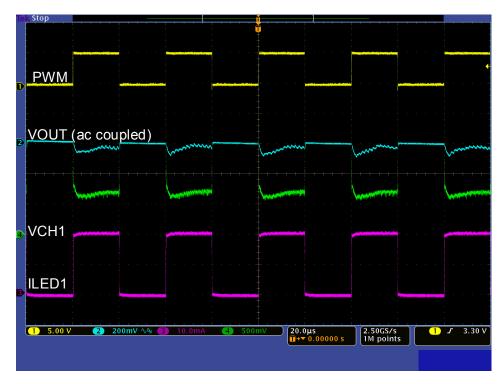

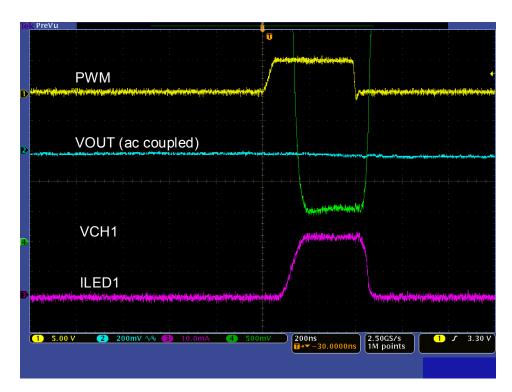

Figure 8. Typical Operating Waveforms (FPWM = 25 kHz, 50% duty)

Figure 9. Low Duty Dimming Operation Waveforms (FPWM = 25 kHz, 1% duty)

# **6** Typical Applications

## 6.1 Application Diagram

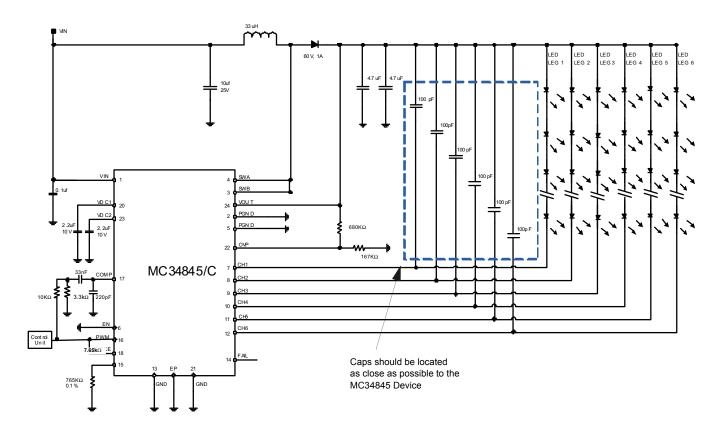

Figure 10. Typical Application Circuit for Single Wire Control,  $f_S$  = 600 KHz ( $V_{IN}$  = 9.0 V,  $I_{LED}$ /channel = 20 mA/channel, 10 LEDs/channel, OVP = 35 V,  $V_{PWM}$  = 3.3 V)

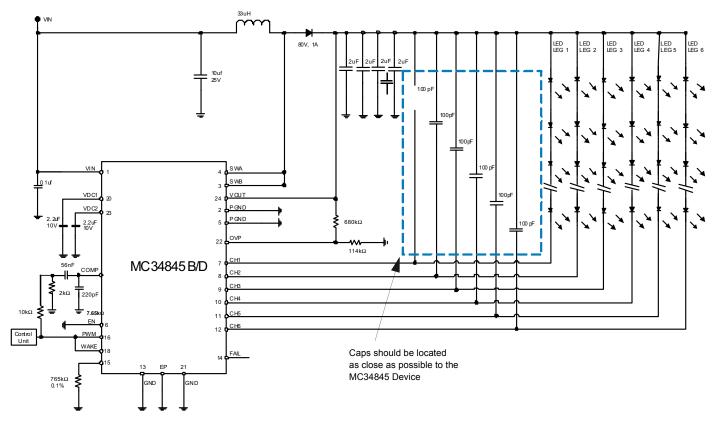

Figure 11. Typical Application Circuit for Single Wire Control,  $f_S$  = 300 kHz ( $V_{IN}$  = 8.0V,  $I_{LED}$  = 20 mA/channel, 14 LEDs/channel, OVP = 49V,  $V_{PWM}$  = 3.3V)

## 6.2 Components Calculation

The following formulas are intended for the calculation of all external components related with the boost converter and network compensation. To calculate the duty cycle, the internal losses of the MOSFET and diode should be taken into consideration:

$$D = \frac{V_{OUT} + V_D - V_{IN}}{V_{OUT} + V_D - V_{SW}}$$

The average input current depends directly on the output current when the internal switch is off.

$$I_{IN-AVG} = \frac{I_{OUT}}{1-D}$$

#### 6.2.1 Inductor

For calculating the Inductor, consider the losses of the internal switch and winding resistance of the inductor:

$$L = \frac{(V_{\rm IN} - V_{\rm SW} - (I_{\rm IN-AVG} \times R_{\rm INDUCTOR})) \times D}{I_{\rm IN-AVG} \times r \times F_{\rm SW}}$$

It is important to look for an inductor rated at least for the maximum input current:

$$I_{\text{IN-MAX}} = I_{\text{IN-AVG}} + \frac{V_{\text{IN}} \times (V_{\text{OUT}} - V_{\text{IN}})}{2 \times L \times F_{\text{SW}} \times V_{\text{OUT}}}$$

#### 6.2.2 Input Capacitor

The input capacitor should handle at least the following RMS current.

$$I_{RMS-C_{IN}} = \left(\frac{V_{IN} \times (V_{OUT} - V_{IN})}{2 \times L \times F_{SW} \times V_{OUT}}\right) \times 0.3$$

#### 6.2.3 Output Capacitor

For the output capacitor selection the transconductance should be taken in consideration.

$$C_{\mbox{OUT}} = \frac{R_{\mbox{COMP}} \times 5 \times G_{\mbox{M}} \times I_{\mbox{OUT}} \times L}{(1-D) \times V_{\mbox{OUT}} \times 0.35}$$

The output voltage ripple ( $\Delta V_{OUT}$ ) depends on the ESR of the Output capacitor. For a low output voltage ripple, it is recommended to use ceramic capacitors which have a very low ESR. Since ceramic capacitor are costly, electrolytic or tantalum capacitors can be mixed with ceramic capacitors for a less expensive solution.

$$\text{ESR}_{C_{OUT}} = \frac{V_{OUT} \times \Delta V_{OUT} \times F_{SW} \times L}{V_{OUT} \times (1 - D)}$$

The output capacitor should at least handle the following RMS current.

$$I_{RMS-C_{OUT}} = I_{OUT} \times \sqrt{\frac{D}{1-D}}$$

### 6.2.4 Network Compensation

Since this Boost converter is current controlled, a Type II compensation is needed. Note that before calculating the network compensation, all boost converter components need to be known. For this type of compensation it is recommended to push out the Right Half Plane Zero to higher frequencies where it does not significantly affect the overall loop.

$$f_{RHPZ} = \frac{V_{OUT} \times (1 - D)^2}{I_{OUT} \times 2\pi \times L}$$

The crossover frequency must be set much lower than the location of the Right half plane zero:

$$f_{CROSS} = \frac{f_{RHPZ}}{5}$$

Since the system has a fixed slope compensation,  $R_{COMP}$  should be fixed for all configurations, i.e.  $R_{COMP}$  = 2.0 k $\Omega$   $C_{COMP1}$  and  $C_{COMP2}$  should be calculated as follows:

$$C_{COMP1} = \frac{2}{\pi \times f_{CROSS} \times {}^{R}COMP}$$

$$C_{COMP2} = \frac{2G_{M}}{6.28 \times F_{SW}}$$

The recommended values of these capacitors for an acceptable performance of the system in different operating conditions are  $C_{COMP1} = 33$  nF and  $C_{COMP2} = 220$  pF.

A resistor network can be implemented from the PWM pin to ground with a connection to the compensation network, to improve the transient response of the boost. This configuration should inject a 1.0 V signal to the COMP pin and the equivalent Thevenin resistance of the divider should be close to  $R_{COMP}$ , (i.e. for 2.0 k $\Omega$  COMP resistor,  $R_{COMP} = 3.3$  k $\Omega$  and  $R_{SHUNT} = 10$  k $\Omega$ . See Figure 10 and Figure 11 for implementation guidelines.

If a faster transient response is needed, a higher voltage (e.g. 1.3V) should be injected to the COMP pin; so the resistor divider should be modified accordingly, but keeping the equivalent Thevenin resistance of the divider close to R<sub>COMP</sub>.

#### 6.2.5 Variable definition

D = Duty cycle

V<sub>OUT</sub> = Output voltage

V<sub>D</sub> = Diode voltage

V<sub>IN</sub> = Input voltage

V<sub>SW</sub> = Internal switch voltage drop.

$\Delta V_{OUT}$  = Output voltage ripple

I<sub>IN-AVG</sub> = Average input current = I<sub>L-AVG</sub>

I<sub>OUT</sub> = Output current

$I_{IN-MAX}$  = Maximum input current

r = Current ripple ratio at the inductor =  $\Delta I_L / I_{L-AVG}$

I<sub>RMS-CIN</sub>= RMS current for the input capacitor

I<sub>RMS-COUT</sub>= RMS current for output capacitor

L = Inductor.

R<sub>INDUCTOR</sub>= Inductor winding resistor

F<sub>SW</sub>= Boost switching frequency

C<sub>OUT</sub> = Output capacitor

R<sub>COMP</sub> = Compensation resistor

G<sub>M</sub>= OTA transconductance

ESR<sub>COUT</sub>= ESR of the output capacitor

f<sub>RHPZ</sub>= Right half plane zero frequency

f<sub>CROSS</sub>= Crossover frequency

C<sub>COMP1</sub>= Compensation capacitor

C<sub>COMP2</sub>= Shunt compensation capacitor

#### 6.2.6 Component Suggestions

The Component Suggestions only apply to the conditions shown. Therefore, adjustments are necessary for different application conditions.

**Table 5. Component Suggestion Table**

| Application<br>Case | V <sub>IN</sub> (min) | V <sub>IN</sub> (Max) | V <sub>O</sub> (max) | VOVP | f <sub>BOOST</sub> | ILED per<br>channel | R <sub>OVP_UPPER</sub> | R <sub>OVP_LOWER</sub> |

|---------------------|-----------------------|-----------------------|----------------------|------|--------------------|---------------------|------------------------|------------------------|

| 1                   | 9.0 V                 | 12 V                  | 30 V                 | 35 V | 600 kHz            | 20 mA               | 680 kΩ                 | 167 kΩ                 |

| 2                   | 6.0 V                 | 12 V                  | 43 V                 | 48 V | 300 kHz            | 23 mA               | 680 kΩ                 | 114 kΩ                 |

| Application<br>Case | L(min)               | L(min)<br>Continuous<br>mode | C <sub>IN</sub> (min) | C <sub>OUT</sub> (min)    | R <sub>COMP</sub> at<br>V <sub>PWM =3.3V</sub> | R <sub>SHUNT</sub> at<br>V <sub>PWM</sub> =3.3 v | C <sub>COMP1</sub> | C <sub>COMP2</sub> |

|---------------------|----------------------|------------------------------|-----------------------|---------------------------|------------------------------------------------|--------------------------------------------------|--------------------|--------------------|

| 1                   | 22 μΗ                | 33 μΗ                        | 1x10 μF; X7R;<br>25 V | 2 x 4.7 μF;<br>X7R; 50 V  | 3.3 kΩ                                         | 10 kΩ                                            | 33 nF              | 220 pF             |

| 2                   | 22 μΗ                | 33 μΗ                        | 1x10 μF; X7R;<br>25 V | 4 x 2.2 μF;<br>X7R; 100 V | 2.0 kΩ                                         | 16 kΩ                                            | 56 nF              | 220 pF             |

|                     | I <sub>SAT</sub> mir | n = 2.6 A                    |                       |                           |                                                |                                                  |                    |                    |

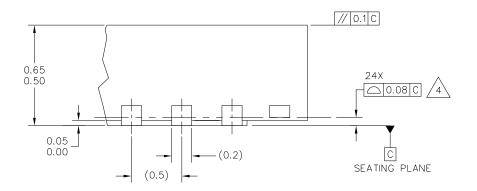

## 7 Packaging

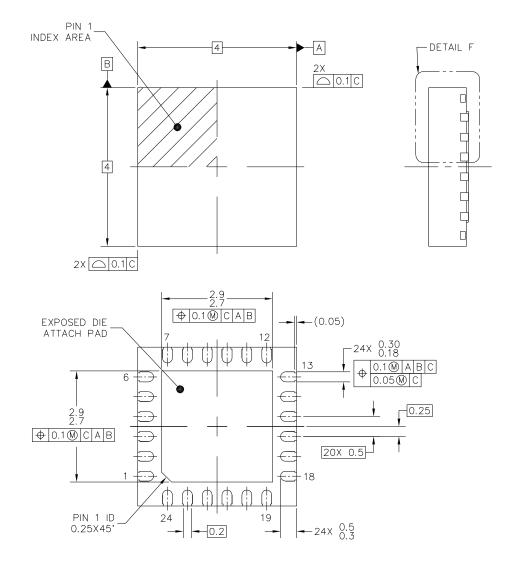

## 7.1 Package Mechanical Dimensions

Package dimensions are provided in package drawings. To find the most current package outline drawing, go to <a href="https://www.freescale.com">www.freescale.com</a> and perform a keyword search for the drawing's document number.

Table 6. Packaging Information

| Package       | Suffix | Package Outline Drawing Number |

|---------------|--------|--------------------------------|

| 24-Pin QFN-EP | EP     | 98ASA00602D                    |

| © FREESCALE SEMICONDUCTOR, INC. ALL RIGHTS RESERVED. | MECHANICAL OU   | TLINE   | PRINT VERSION NOT TO | ) SCALE  |

|------------------------------------------------------|-----------------|---------|----------------------|----------|

| TITLE:                                               |                 | DOCUMEN | NT NO: 98ASA00602D   | REV: 0   |

| QFN, THERMALLY ENF<br>4 X 4 X 0.58, 0.5 PITCH.       |                 | STANDAF | RD: NON-JEDEC        |          |

| 7 X 7 X 8.38, 8.8 111611,                            | 2 1 121(1)11(1) |         | 09                   | JUL 2013 |

DETAIL F VIEW ROTATED 90°CW

| © FREESCALE SEMICONDUCTOR, INC.<br>ALL RIGHTS RESERVED. | MECHANICAL OU                           | TLINE   | PRINT VERSION NO   | T TO SCALE  |

|---------------------------------------------------------|-----------------------------------------|---------|--------------------|-------------|

| TITLE:                                                  |                                         | DOCUME  | NT NO: 98ASA00602D | REV: 0      |

| QFN, THERMALLY EN<br>4 X 4 X 0.58, 0.5 PITCH.           |                                         | STANDAF | RD: NON-JEDEC      |             |

| 7 7 7 7 0.30, 0.3 111011,                               | 21 121111111111111111111111111111111111 |         |                    | 09 JUL 2013 |

#### NOTES:

- 1. ALL DIMENSIONS ARE IN MILLIMETERS.

- 2. DIMENSIONING AND TOLERANCING PER ASME Y14.5M-1994.

- 3. THIS IS A NON-JEDEC REGISTERED PACKAGE.

A COPLANARITY APPLIES TO LEADS AND DIE ATTACH FLAG.

5. MIN. METAL GAP SHOULD BE 0.2 MM.

| © FREESCALE SEMICONDUCTOR, INC. ALL RIGHTS RESERVED.                   | MECHANICAL OU | TLINE               | PRINT VERSION NO   | T TO SCALE  |

|------------------------------------------------------------------------|---------------|---------------------|--------------------|-------------|

| TITLE:  QFN, THERMALLY ENHANCED,  4 X 4 X 0.58, 0.5 PITCH, 24 TERMINAL |               | DOCUMEN             | NT NO: 98ASA00602D | REV: 0      |

|                                                                        |               | STANDARD: NON-JEDEC |                    |             |

|                                                                        |               |                     |                    | 09 JUL 2013 |

# Revision History

| Revision | Date    | Description of Changes                                                                                                                                                    |  |

|----------|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 6.0      | 12/2011 | <ul> <li>Changed the max rating for the OVP pin from 7.0V to 7.75V in the Absolute Maximum Ratings Table on page 6.</li> <li>Updated Freescale form and style.</li> </ul> |  |

| 7.0      | 6/2014  | No technical changes. Revised back page. Updated document properties. Added SMARTMOS sentence to first paragraph.                                                         |  |

| 8.0      | 5/2015  | <ul> <li>Removed obsolete part numbers from Orderable Parts</li> <li>Updated Packaging</li> <li>Updated Freescale form and style</li> </ul>                               |  |

How to Reach Us:

Home Page:

free scale.com

Web Support:

free scale.com/support

Information in this document is provided solely to enable system and software implementers to use Freescale products. There are no express or implied copyright licenses granted hereunder to design or fabricate any integrated circuits based on the information in this document.

Freescale reserves the right to make changes without further notice to any products herein. Freescale makes no warranty, representation, or guarantee regarding the suitability of its products for any particular purpose, nor does Freescale assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation consequential or incidental damages. "Typical" parameters that may be provided in Freescale data sheets and/or specifications can and do vary in different applications, and actual performance may vary over time. All operating parameters, including "typicals," must be validated for each customer application by customer's technical experts. Freescale does not convey any license under its patent rights nor the rights of others. Freescale sells products pursuant to standard terms and conditions of sale, which can be found at the following address: freescale.com/SalesTermsandConditions.

Freescale and the Freescale logo are trademarks of Freescale Semiconductor, Inc., Reg. U.S. Pat. & Tm. Off. SMARTMOS is a trademark of Freescale Semiconductor, Inc. All other product or service names are the property of their respective owners.

© 2015 Freescale Semiconductor, Inc.

Document Number: MC34845

Rev. 8.0 5/2015