### Freescale Semiconductor Application Note

AN4177 Rev. 2.0, 1/2011

# Repetitive Clamped Inductive Energy Capability (for the MC10XS3535)

By: Laurent Guillot

## 1 Introduction

This document describes the functioning of the 10XS3535 smart power switch when switching inductive loads with no freewheeling diode. Also known as Clamp Inductive Switching (CIS), in this case.

The 10XS3535 is one in a family of devices designed for low-voltage automotive lighting applications. Its five low RDS(ON) MOSFETs (triple  $10m\Omega$  and dual  $35m\Omega$ ) can control five separate 55W / 28W bulbs, and/or Xenon modules, and/or LEDs.

Programming, control and diagnostics are accomplished using a 16-bit SPI interface. Its output, with selectable slew-rate, improves electromagnetic compatibility (EMC) behavior. Additionally, each output is controlled through SPI for pulse-width modulation (PWM). The 10XS3535 is programable via the Serial Peripheral Interface (SPI), the fault current trip levels, and duration of acceptable lamp inrush. The device has Fail-safe mode to provide safe functionality of the outputs in case of MCU damaged.

For feature information, refer to the MC10XS3535 data sheet.

### Contents

| 1 | Introduction 1                      |

|---|-------------------------------------|

| 2 | Negative Output Clamp Description 2 |

| 3 | Mono-Pulse CIS                      |

| 4 | Repetitive Output Switching 5       |

| 5 | <b>References</b>                   |

| 6 | Revision History 7                  |

© Freescale Semiconductor, Inc., 2010 - 2011. All rights reserved.

**Negative Output Clamp Description**

## 2 Negative Output Clamp Description

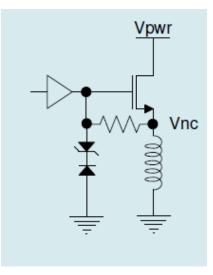

At each ON to OFF transition, the demagnetization of inductive load is done through the N-Channel MOSFET as described in **Figure 1**:

Figure 1. Simplified block Diagram

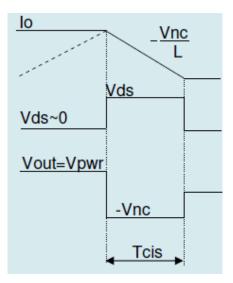

Figure 2. Output Switching Waveforms

The steady-state output voltage is clamped at -Vnc (-18V typ.) and is not dependent on temperature and current. In the case of Tcis (=lo x L / Vnc) > 1msec, the waveforms can be simplified with a rectangle as shown in Figure 2. The energy dissipated in the N-Channel MOSFET is:

Formula [1]:  $E = \frac{1}{2} x L x Io^{2} x (1 + Vpwr / Vnc)$

# 3 Mono-Pulse CIS

### 3.1 Mono-pulse CIS test to fail

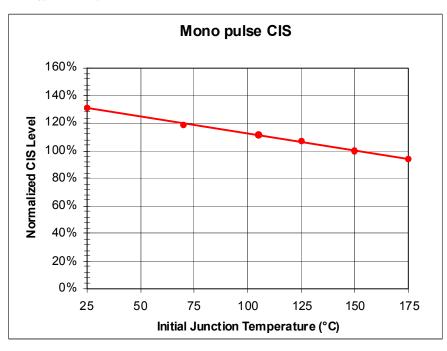

The CIS device capability depends on electrical parameters mentioned in **Formula [1]**, but the initial junction temperature (T<sub>J</sub>) is a key contributor. In **Figure 3**, a decreasing application ambient temperature will gain more margin of device CIS energy capability.

### Figure 3. CIS Level Over Junction Temperature

**Table 1** presents an example of an experimental destructive CIS level obtained for VPWR=14V and  $T_J$ =125°C (10 fresh-out samples were used per test - part soldered on 4 layers PCB with Rthja=18°/W).

| Table 1. Maximum CIS Level for 10m $\Omega$ Cha | nnel |

|-------------------------------------------------|------|

|                                                 |      |

| Inductive load value | Peak current | Energy dissipated in the N-channel MOSFET |

|----------------------|--------------|-------------------------------------------|

| 300µH                | 35.7A        | 497mJ during 0.6μ sec                     |

| 16mH                 | 6.23A        | 634mJ during 5.5msec                      |

### 3.2 Mono-pulse CIS level tested in production

Freescale uses the following procedure to guarantee the CIS level during a vehicles life-time (15 years):

- The 10XS3535 parts are tested at 200mJ at T<sub>J</sub>=125°C in production (2 times higher in regards to the specified level).

- The CIS energy capabilities are checked at 110mJ at T<sub>J</sub>=125°C at the end of the accelerated ageing tests defined by AECQ100 Standard.

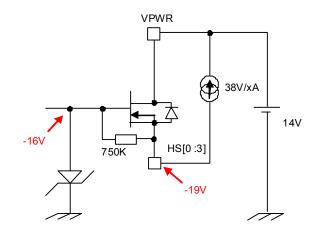

**Figure 4** describes the test configuration used in production. A current source pulls the source of the MOSFET to a value lower than GND. When applying 38V between the source and drain, the internal circuitry of the control die will clamp the device to around -18V and the gate/source voltage will allow the MOS to turn On the driving current. The time duration will be set to match 200mJ (or 110mJ) energy dissipation (T = 200/((VCL+VPWR)\*IOUT)) = pulse duration in ms. The energy pulse is applied at each output separately.

**Figure 4. Production Test Configuration**

## 4 Repetitive Output Switching

In the case of repetitive N-Channel MOSFET switching, the failure process is no longer operative and the fatigue-induced ageing mainly affects the active region of the N-Channel MOSFET. Usually the top metal and AI wire bonds.

### 4.1 Tests to Pass

**Table 2** summarizes the repetitive switching "tests-to-pass" which were done for the  $10m\Omega$  channel (10 fresh-out samples per test were tested - part soldered on 4 layers PCB with Rthja=18°/W).

| Test Name                                                             | Condition                               | Number of cycles without failure |

|-----------------------------------------------------------------------|-----------------------------------------|----------------------------------|

| <b>1- Operating Life Time</b><br>T <sub>J</sub> range: -40°C to +85°C | 100W lamp inrush<br>42A DC during 5msec | 2.5Mio                           |

| <b>2- Overload</b><br>@ T <sub>J</sub> =70°C initial                  | 60A DC / 20msec<br>30A DC / 150msec     | 250k<br>250k                     |

| 3- Over-current Shutdown<br>@ T <sub>J</sub> =70°C initial            | 92.8A peak / 250µsec                    | 250k                             |

| <b>4- Hard short-circuit</b><br>@ T <sub>J</sub> =70°C initial        | 40A peak / 150µsec                      | 500k<br>500k                     |

Table 2. Repetitive Switching Tests for 10m $\Omega$  Channel

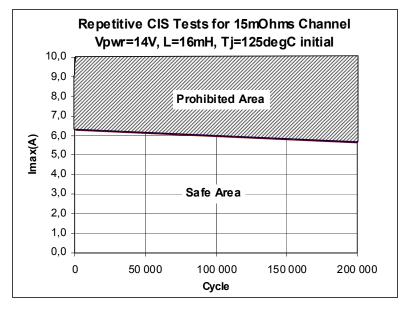

### 4.2 CIS Tests to Fail

Some "tests-to-fail" were completed for repetitive CIS condition in order to determine the prohibited area for  $15m\Omega$  channel with 16mH inductive load at  $T_J=125^{\circ}$ C initial. The off-state duration time was defined to guarantee that junction temperature came back to initial value before the next output switching. **Figure 5** depicts the safe area based on experimental trials using a  $15m\Omega$  channel (fresh-out samples soldered on 4 layered PCB with Rthja=18°/W).

Note: the energy dissipated in the N-Channel MOSFET is 430mJ during 4.7msec.

Figure 5. Safe Area for 15m $\Omega$  Channel Repetitive CIS Operation

References

## **5** References

MC10XS3535 Data Sheet - Smart Front Corner Light Switch (Triple  $10m\Omega$  and Dual  $35m\Omega$ )

# 6 Revision History

| Revision | Date | Description of Changes                                                                |

|----------|------|---------------------------------------------------------------------------------------|

| 1.0      |      | Initial Release                                                                       |

| 2.0      |      | Corrected typographical error on footers of pages 2 through 7 - no technical changes. |

### How to Reach Us:

### Home Page:

www.freescale.com

Web Support: http://www.freescale.com/support

#### **USA/Europe or Locations Not Listed:**

Freescale Semiconductor, Inc. Technical Information Center, EL516 2100 East Elliot Road Tempe, Arizona 85284 1-800-521-6274 or +1-480-768-2130 www.freescale.com/support

### Europe, Middle East, and Africa:

Freescale Halbleiter Deutschland GmbH Technical Information Center Schatzbogen 7 81829 Muenchen, Germany +44 1296 380 456 (English) +46 8 52200080 (English) +49 89 92103 559 (German) +33 1 69 35 48 48 (French) www.freescale.com/support

#### Japan:

Freescale Semiconductor Japan Ltd. Headquarters ARCO Tower 15F 1-8-1, Shimo-Meguro, Meguro-ku, Tokyo 153-0064 Japan 0120 191014 or +81 3 5437 9125 support.japan@freescale.com

#### Asia/Pacific:

Freescale Semiconductor China Ltd. Exchange Building 23F No. 118 Jianguo Road Chaoyang District Beijing 100022 China +86 10 5879 8000 support.asia@freescale.com

#### For Literature Requests Only:

Freescale Semiconductor Literature Distribution Center P.O. Box 5405 Denver, Colorado 80217 1-800-441-2447 or +1-303-675-2140 Fax: +1-303-675-2150 LDCForFreescaleSemiconductor@hibbertgroup.com Information in this document is provided solely to enable system and software implementers to use Freescale Semiconductor products. There are no express or implied copyright licenses granted hereunder to design or fabricate any integrated circuits or integrated circuits based on the information in this document.

Freescale Semiconductor reserves the right to make changes without further notice to any products herein. Freescale Semiconductor makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does Freescale Semiconductor assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation consequential or incidental damages. "Typical" parameters that may be provided in Freescale Semiconductor data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals", must be validated for each customer application by customer's technical experts. Freescale Semiconductor does not convey any license under its patent rights nor the rights of others. Freescale Semiconductor products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the Freescale Semiconductor product could create a situation where personal injury or death may occur. Should Buyer purchase or use Freescale Semiconductor products for any such unintended or unauthorized application, Buyer shall indemnify and hold Freescale Semiconductor and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that Freescale Semiconductor was negligent regarding the design or manufacture of the part.

Freescale <sup>™</sup> and the Freescale logo are trademarks of Freescale Semiconductor, Inc. All other product or service names are the property of their respective owners. © Freescale Semiconductor, Inc., 2010 - 2011. All rights reserved.

AN4177 Rev. 2.0 1/2011