Building a System Verilog Universal Verification Component with the Incisive Plan-to-Closure Methodology

Session 2.12

David Long, John Aynsley and Jonathan Bromley, Doulos

# **Building a SystemVerilog Universal Verification Component**

#### **CONTENTS**

- Introduction

- The Verification Plan

- Assertions, Coverage and Constraints

- SystemVerilog Testbench Architecture

# **SystemVerilog for Verification**

- SystemVerilog has verification features not found in VHDL or Verilog:

- Assertions and a temporal sequence language

- Functional coverage

- Constrained random test vectors

- Dynamic creation of transaction objects

- Extensible classes for verification components and transactions

- Features to avoid simulation races between test bench and DUT

- But can be a steep learning curve for RTL/HDL designers

- Some sort of framework for block-level test benches would help ...

# **Incisive Plan-to-Closure Methodology**

URM (Universal Reuse Methodology) / "Design Team Verification"

- Module-Based with Classes URM

- SystemVerilog verification environment

- Classes for transaction objects

- Does not require expertise in OOP (polymorphism, virtual methods, etc)

- Guidelines to create reusable Universal Verification Components (UVCs)

Our experience of actually getting this to work ...

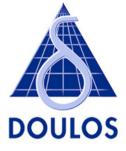

# **System to be Verified**

- Bus-based sub-system with CPU

- CPU, Serial IO and arbiter are RTL SystemVerilog

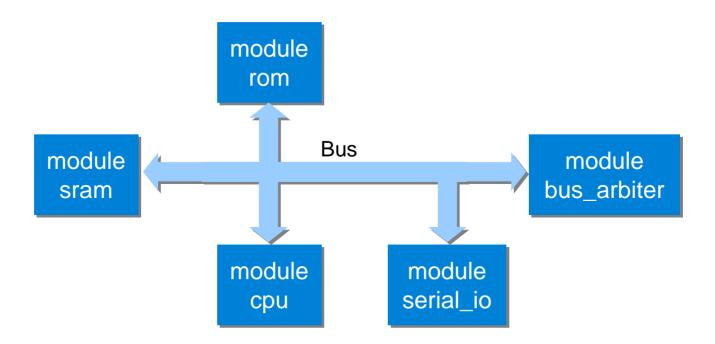

#### **UVC** used with Verification Plan

- Identify key requirements and verification strategy for each requirement <u>before</u> starting to develop testbench!

- Assertion-Based Verification uses SystemVerilog property to continuously check design behaviour, e.g. interface protocol

Following a write there must not be a read for at least 1 clock cycle.

The write enables should each stay high for only one clock cycle

Coverage-Driven Verification - uses SystemVerilog covergroup to record how many times a condition has been met

> Forward and backward jump operations for every step in the range 1 to 15 should be exercised.

#### **The Verification Process**

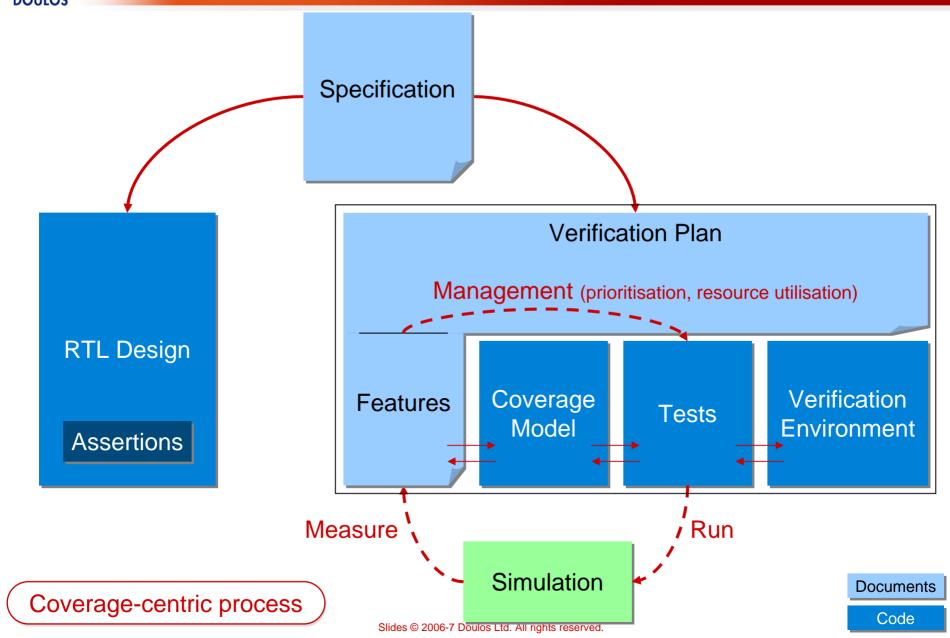

#### From Features to Tests

- Features grouped by specification, implementation, and functionality

- Many-to-many mapping between features and coverage points

- Coverage and tests implemented in verification language or scripts

- Grade tests by coverage achieved, bugs found, run times etc

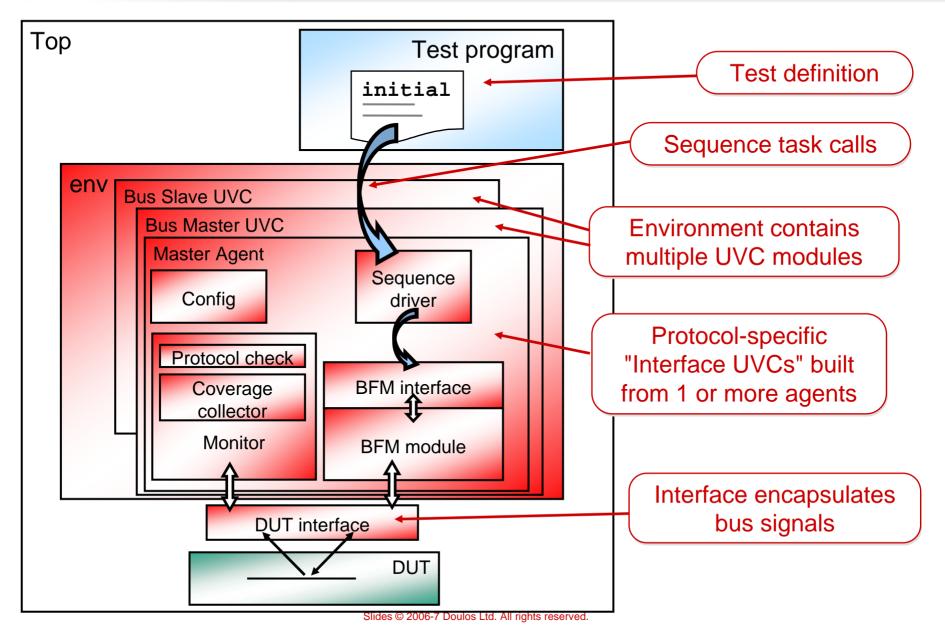

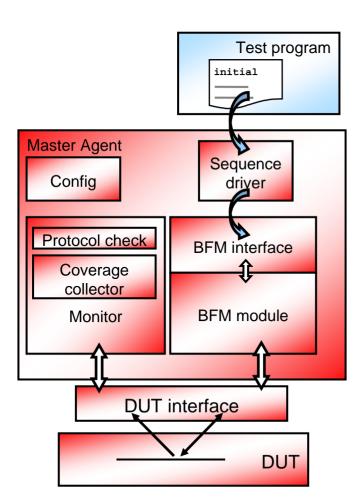

#### **URM Testbench Structure**

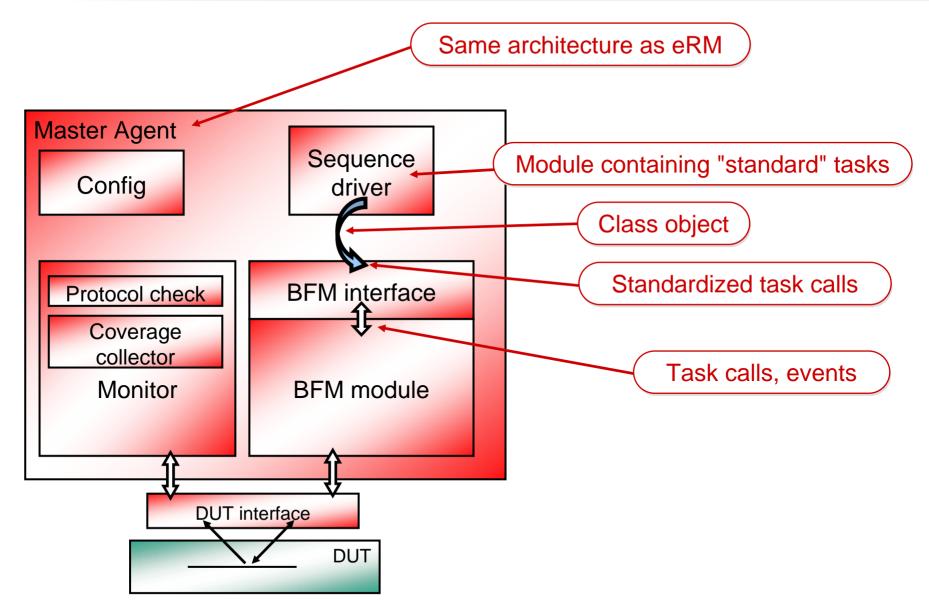

# Agent in SystemVerilog URM

# **Sequence Pushes Transactions**

```

module ex seq driver m

( ex bfm if bfm if );

ex_bfm_trans_c cur_trans;

Template for new transactions

task simple ( ... );

ex bfm trans c trans;

trans = new cur trans;

assert(trans.randomize());

bfm if.put ( trans );

Independent of

endtask : simple

BFM details

task scenario x ( ... );

simple ( ... );

Sequence built from

other sequences

```

#### **Transaction Class**

```

tx ...

min_delay 1

max_delay 15

enable_

delay_

constraint 1

tx_delay_

range ...

```

```

class ex bfm trans c;

rand ex_bfm_trans_s tx;

Transaction data struct

int min delay;

Control

int max delay;

bit enable delay constraint;

constraint tx_delay_range {

Constraint

if (enable delay constraint)

tx.delay inside{[min_delay:max_delay]};

function new();

Constructor

min delay = 1;

endclass: ex bfm trans c

```

#### **Derived Transaction Class**

```

class derived_trans_c extends ex_bfm_trans_c;

constraint tx delay odd {

Additional constraint

if (enable delay constraint)

tx.delay[0] == 1;

function new();

super.new();

Calls base class constructor

Handle can point to derived class

task simple ( ... );

ex bfm trans c trans;

Shallow copy

trans = new cur trans; +

assert(trans.randomize());

Includes derived class constraints

```

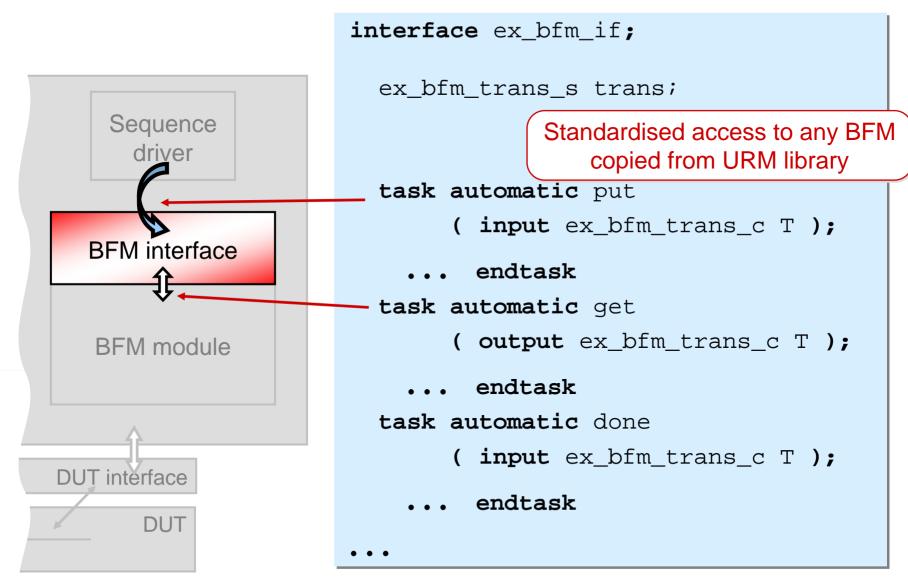

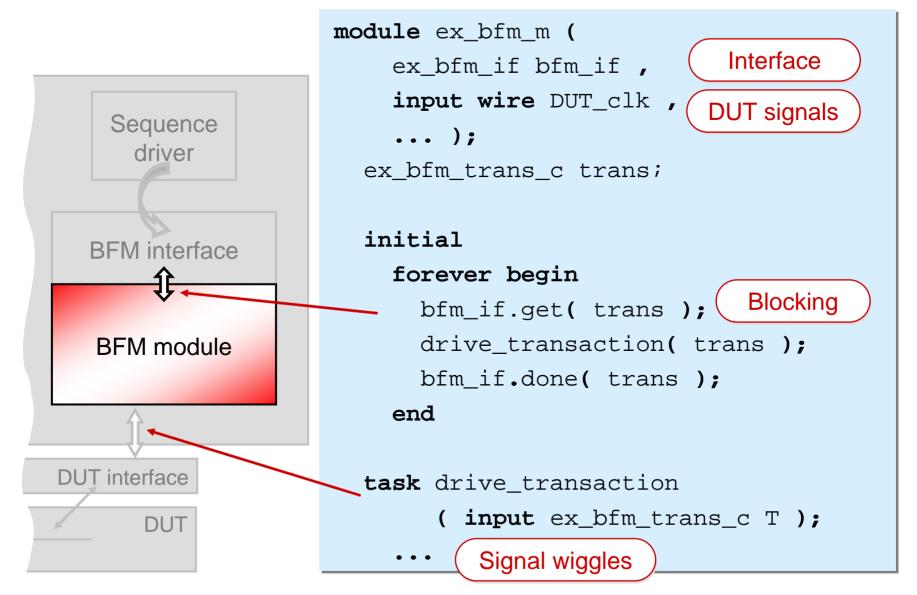

#### The BFM Interface

#### **BFM Pulls Transactions**

# **Monitor Detects Bus Activity**

```

module ex bus mon m (

input wire DUT clk , ...);

mem write: cover property (

@(posedge DUT clk)

first match(

bus if.wr

##1[1:$]

bus if.wack )

) cover_mem_wr(bus_if.addr, ...);

Called when sequence matches

property after we;

@(posedge bus if.clk) disable iff

(bus if.reset)

bus_if.we |=> (

!bus_if.we && !bus_if.re);

endproperty: after_we

assert property (after we);

```

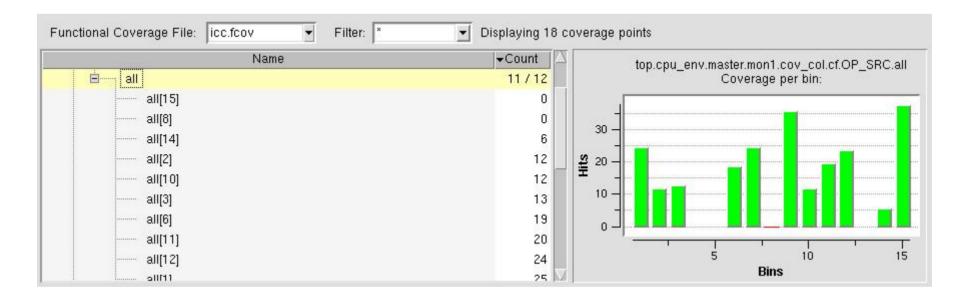

# **Functional Coverage**

- Coverage points do not reveal how conditions are met

- SystemVerilog covergroup can record sampled value occurrence in bins and cross-coverage between coverpoint pairs to measure "Functional" coverage

- Performed by coverage collector module

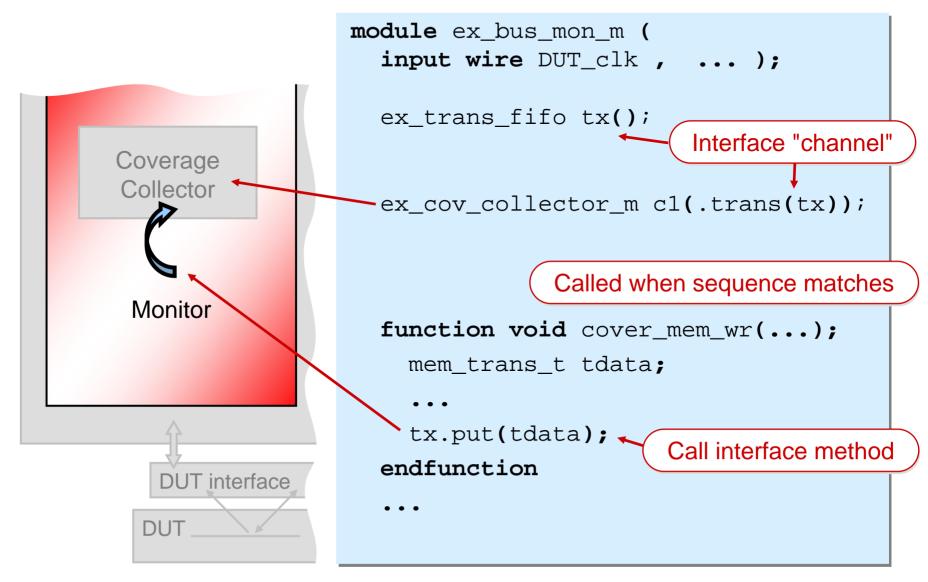

# **Writing to Coverage Collector**

# **The Coverage Collector**

```

module ex cov collector m (

ex trans fifo trans);

addr t addr cp;

Mirror registers

mode t rw cp; ...

covergroup cov mem acc;

mon addr: coverpoint addr cp {

bins all[] = { [0:15] };

ignore_bins bad = {0,5,8}; }

mem w: cross mon addr, mon rw;

endgroup

cov mem acc mem c = new;

Instance

always

begin ...

Blocking

trans.get(tx);

addr = tx.addr;

mem c.sample();

```

### program vs. module

#### SystemVerilog program-level code:

- program

- Randomization, classes

- Postponed sampling and updating

- Dynamic creation of objects

#### SystemVerilog module-level code:

- module, interface

- Verilog simulation semantics

- Static object hierarchy

# **Test Configuration and Control**

```

program test p();

initial

begin

randcase

60: begin

Transaction template

derived_trans_c t;

t = new;

env.master.a0.seq_inst.set_generated_trans(t);

end

Sequence generator

40: begin ...

Alternative test cases

endcase

start test();

URM Package methods

#100;

end test();

```

#### Conclusions

- Testbench architecture consists of modules plus a program

- Coding style similar to Verilog and VHDL

- DUT, BFM and sequence driver are independent

- Classes used for transactions only

- Test program can pass randomized transactions to sequence driver

- Does not require expertise in object-oriented programming

- Test program is compact and easy to modify

- Uses "standard" infrastructure provided by UVCs

- Assertions check protocol throughout simulation

- Coverage from properties and covergroups recorded in coverage database

# CONNECT: IDEAS

**CDNLive! 2007 Silicon Valley**