# **Integrating Design IP and** Verification IP– To Ensure Quality and Predictability

Sriram Swaminathan

Principal Engineer ssriram@rambus.com

Rambus Chip Technologies India

#### **Agenda**

- IP Challenges

- Rambus Design IP

- Verification IPs

- Cadence VIP solution

- Rambus VIP

- Cadence-Rambus collaboration

- Interoperability

- Summary

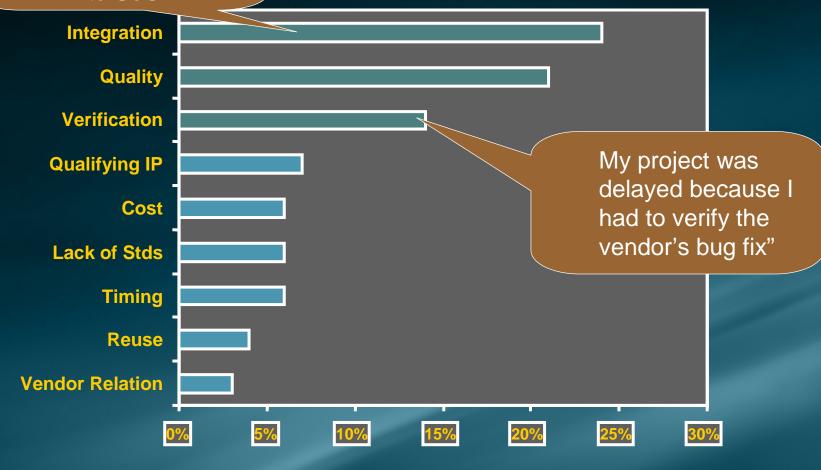

# **IP Challenges**

"I had to spend time integrating the IP into SoC"

Source: Gartner, DAC - 2006

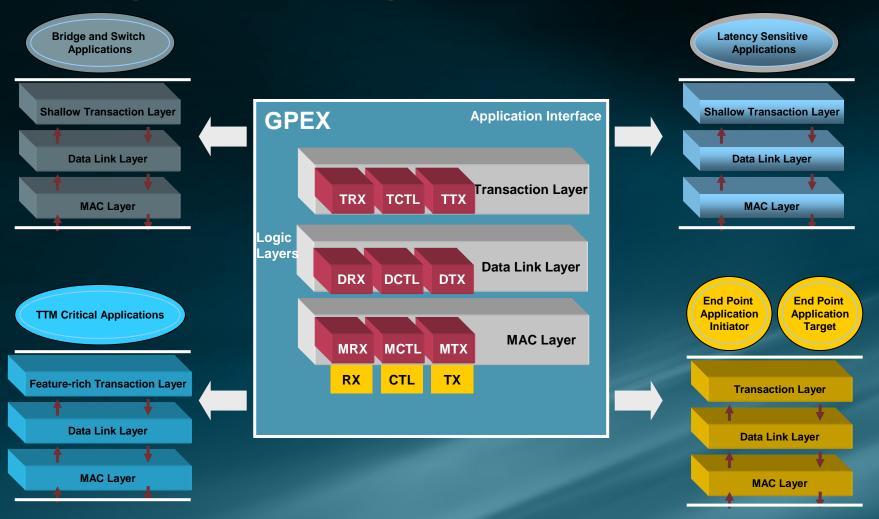

# Challenges for IP providers

- Too much Variability -> configuration explosion

- Application: SOCs, bridges, switches, mobile, server..

- Interfaces: proprietary, VCI, AHB, OCP-IP...

- # of configurations >> 100

- Lack of standards in EDA space

- Languages: Verilog, VHDL, SystemVerilog, e

- Tools: Simulators, HVL engines, formal engines

- Methodology: Cadence, Synopsys, Mentor

- Multiple vendors for Design and VIP

# Challenges for IP consumer

- Correctness of integration

- Correctness of any changes to IP

- Correctness of selected configuration to meet the system goals performance, power..

- Verification after implementation stages

- System level aspects: reset, clock, intr, software access

- Verification of coverage: code, functional...

- Verification of rest of the design through the IP

Is the IP verification environment reusable for the above chip verification tasks?

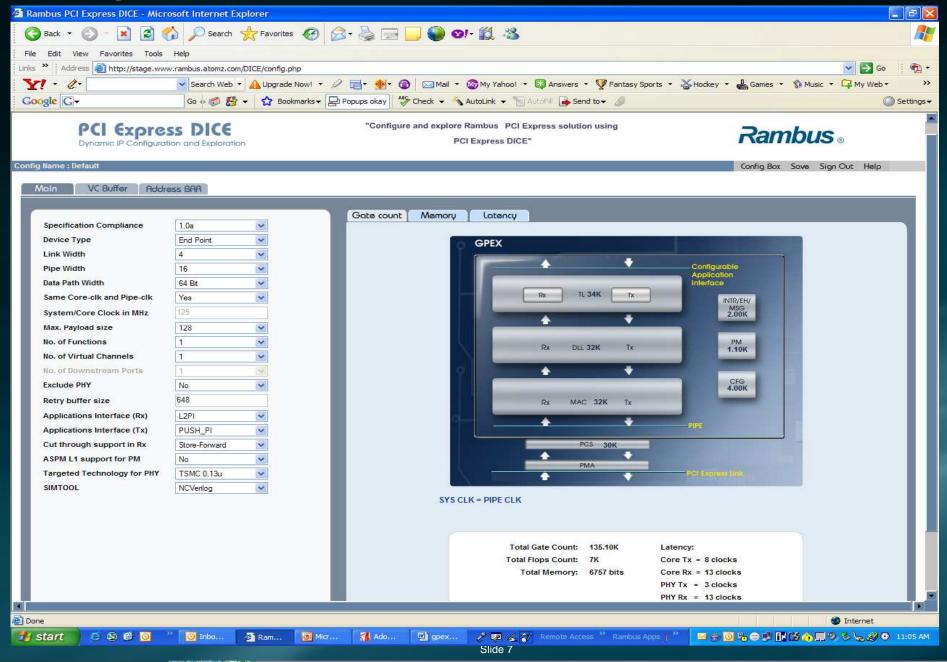

# Rambus - Configurable IP Technology

- Easy IP configuration and integration

- Flexible verification env for all IP configs

- IP fully validated for all the configs

- Quality metrics for all the design modes

- Design aware customization service availability

#### DICE

## **Configurable Design IP Solutions**

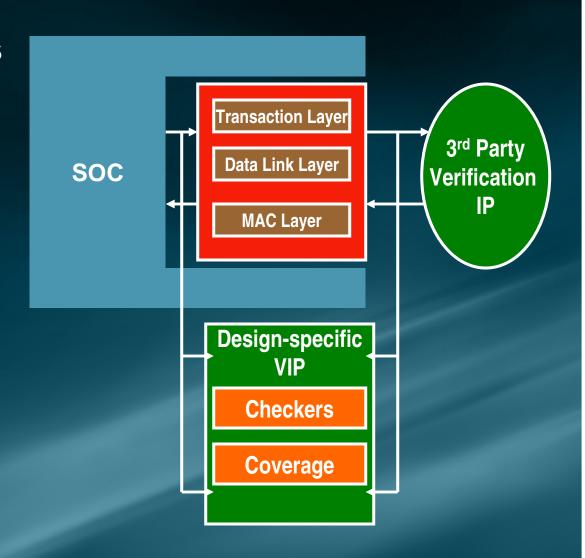

#### **IP Verification requirement**

- Environment needs to be configuration agnostic

- Consider both protocol features and design-specific implementation

- Must be re-usable in SoC environment

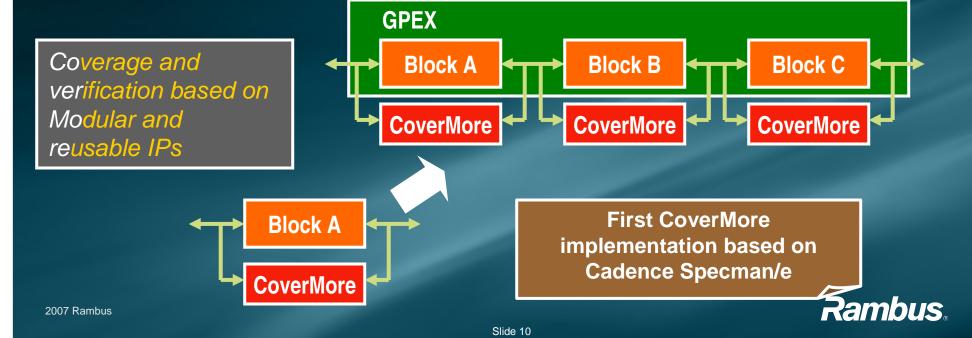

#### Rambus VIP - CoverMore

- CoverMore

- Design-specific VIP

- Highly modular approach

- Reusable across block, IP and chip level

- "Self-checking" Design IP

#### **Cadence VIP Strategy**

**Compliance Mgmt. System**

**UVC**

SystemVerilog Interface  $\mid e \mid$  Interface

Advanced Testbench Core

Transaction-based Acceleration

Incisive Assertion-based VIP

Incisive SpeedBridge<sup>TM</sup>

- Provide Plan-to-Closure VIP spanning full verification process

- Support most complex, demanding protocols

- Unique Compliance Management System

- Enable customers & partners to deploy CDNS's VIP development process

- Provide tailored Verification IP for Cadence Vertical Kits

## Compliance Management System (CMS)

**Automates compliance verification and reporting**

- Leverage Cadence uVC Functional Coverage

- Key differentiator

- Optimized for Rambus IP with Rambus refinements

Executable representation of verification objectives

Reports detailed verification status (Coverage model)

Rambus Specific Refinements

Compliance Management System

Compliance vPlan

Compliance Reporting Compliance

Coverage and

Metrics

Compliance Test Suite

Protocol compliance coverage points and checks

Constrained random sequences automatically reach ~70% coverage

#### **DIP-VIP Interoperability Challenges**

- Ensuring the VIP and Design IP have the same configuration

- In depth design knowledge availability

- Verification IP expertise

- Achieving targeted coverage of Application Interface

- Debugging

- Time consuming Root-cause analysis

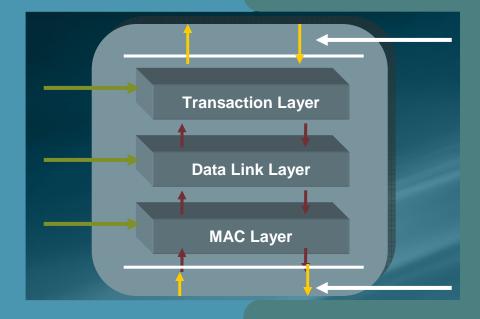

# Cadence-Rambus Collaboration

- Fully Integrated and Independently verified PCIe solution

- Highly adaptable, silicon-proven PCle digital core and Phy IP from Rambus

- Automated and metric-driven VIP from Cadence

- Leverages several years of expertise

Combine configurable, proven design IP with best of class VIP

# **Combining Best of Breed Design and Verification IP**

Concept

Revenue

- Cadence & Rambus value proposition

- Highest quality

- Fastest time to revenue

- Lowest risk

#### **Best of Breed PCI Express Solution**

- Design IP and VIP independently cross checked

- Cadence and Rambus models built independently

- Design IP and VIP most tightly integrated

- **Executable verification plan specific to your IP**

- Customized test suite specific to your IP

- **Automated protocol Compliance Management System**

#### **Integrated Environment**

Targets Design IPspecific Functionality Targets Design IP

Protocol Compliance

and Integration of

Design IP and

Customer Logic

Rambus VIP (CoverMore)

Cadence VIP (CMS)

# Methodology

- Re-create customer environment

- Maintain Verification independence

- Tool aspects

- Follow release QA for eVC and Design IP

- Debugging

- Run regressions at CDN and Rambus

- Regressions include Cadence + Rambus tests

- Root-cause analysis

- VIP/tool anomaly fixes by CDN

- Design IP anomaly fixes by Rambus

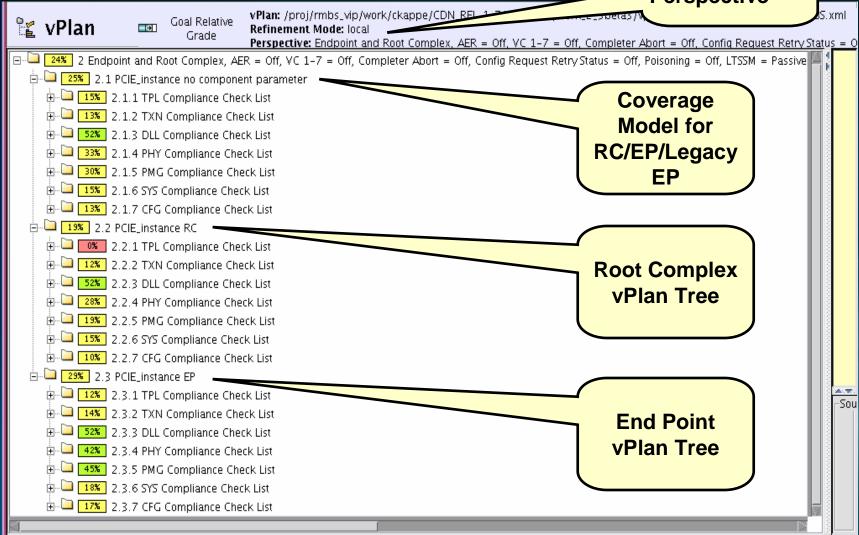

#### Refinement

- CDN PCle compliance vPlan has all features of PCle

- Example DUT configuration specific features

- DUT acts as End point

- RC related coverage points are disabled

- Unsupported PCle compliance points in the design

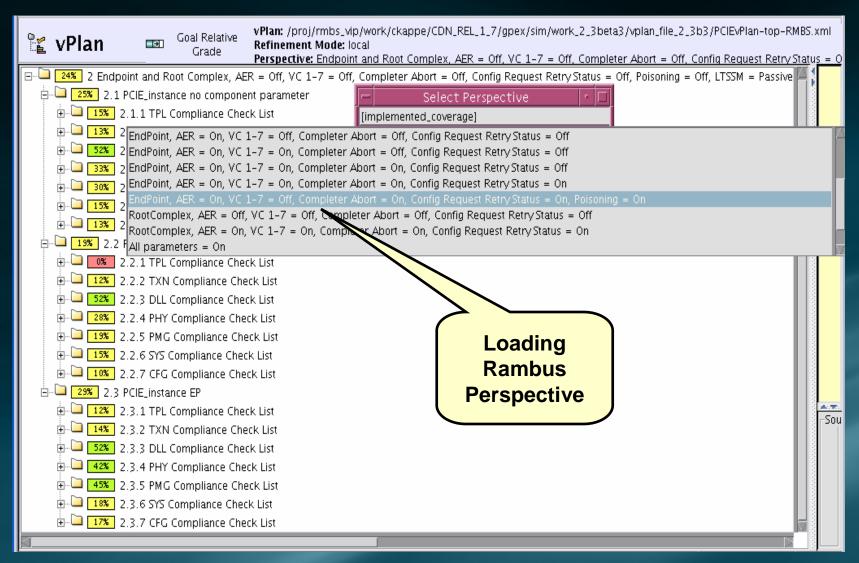

- Refined vPlan and created required perspective which will load on CDN compliance vPlan

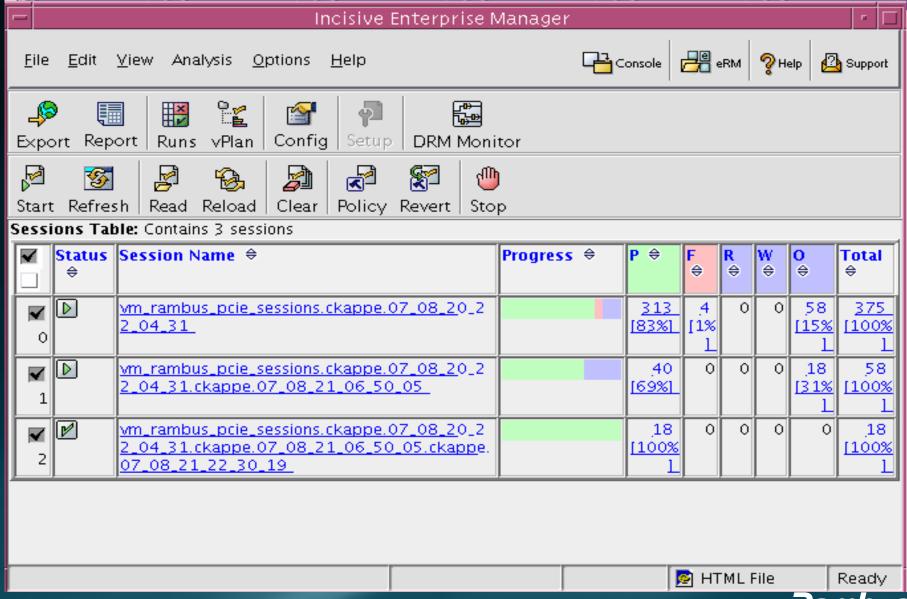

#### vManager Regression Session

Rambus

#### vPlan Default Perspective

Default Perspective

#### vPlan - Loading Rambus Perspective

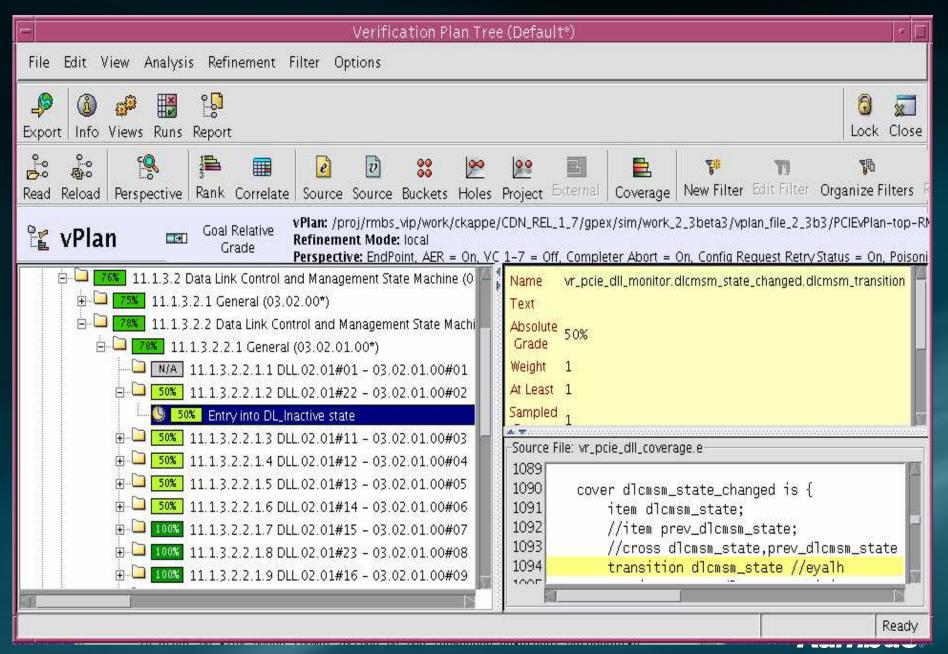

#### vPlan Window - Selected Item

# **Failure Report - First Failure Description**

| Runs [1] (First_Failures) |                                                                                                   |                                                                                                   |                                                                                          |                                                                                            |                                                                  |                             |                            |         |                           |                    |                                                           |                     |            | -   r   _   |  |

|---------------------------|---------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------|------------------------------------------------------------------|-----------------------------|----------------------------|---------|---------------------------|--------------------|-----------------------------------------------------------|---------------------|------------|-------------|--|

| <u>F</u> ile <u>E</u>     | <u>File Edit V</u> iew Analysis <u>O</u> ptions                                                   |                                                                                                   |                                                                                          |                                                                                            |                                                                  |                             |                            |         |                           |                    |                                                           |                     |            |             |  |

| <b>₽</b><br>Export        | <b>ᡌ</b>                                                                                          | <b>⊘</b> a<br>Redo                                                                                | © <b>⊈</b><br>∨Plan                                                                      | <u>(i)</u><br>Info                                                                         | Views                                                            |                             |                            |         |                           |                    |                                                           |                     | []<br>Lock | Close       |  |

| Chart I                   | <b>₽</b><br>Rerun                                                                                 | ∰ı<br>Group                                                                                       | Filter                                                                                   | <b>∰</b><br>Add                                                                            | Select                                                           | <mark>‱</mark> 1<br>Ungroup | <b>Ⅲ</b><br>Unfilter       | Runs    |                           |                    |                                                           |                     |            |             |  |

| Runs                      | Grouped by: First Failure Description Runs Filtered by: Status == failed                          |                                                                                                   |                                                                                          |                                                                                            |                                                                  |                             |                            |         |                           |                    |                                                           |                     |            |             |  |

| Table: C                  | ontains                                                                                           | 4 runs i                                                                                          | n 4 gro                                                                                  | ups (no                                                                                    | o runs are                                                       | e filtered o                |                            | ranc    | u                         |                    |                                                           |                     |            |             |  |

| Run Id<br>≑               | First F                                                                                           | ailure D                                                                                          | escript                                                                                  | ion ⊕                                                                                      |                                                                  |                             | First<br>Failure<br>Kind 👄 | Failure | First<br>Failure<br>Log 🕏 | Top Files <i>⇔</i> |                                                           |                     | Seed ⇔     | Statu!<br>≑ |  |

|                           | D_SIZE, register of P_EP page 3 : CFG.8 wr_pcie Name: VR_PCI Registe VR_PCI wr_ad_I Max_p: Value: | .SUPPOR r In vr_p r In vr_p r TL age 68 Com 3.3#1 Do _tl_pkt- E_DEVIC r: E_DEVIC reg-@14 ayload_S | RTED Implicie_tl_mint. PCIE upliance evice: P. @7459  E_CAPA  E_CAPA  Size Sup alue: 5 F | valid va<br>nonitor<br>Spec :<br>checkl<br>_EP Par<br>Regist<br>ABILITIE<br>Name<br>ported | -@7401<br>: 7.8.3<br>list items<br>cket:<br>er<br>:5<br>:5<br>:: | specman                     | dut_error                  | 6122    | local_log.log<br>-        | /vr_pcie_test_s    | fines/pio_enum<br>suite_top.e<br>:fg_read_initial_regs_va | alue_before_cfq_wri | 171979570  | failed      |  |

| <u>R0029</u> 8<br>-       | PM_ACI<br>althoug<br>recieve<br>disable<br>vr_pcie<br>vr_pcie<br>5.3.2.1<br>checklis              | K_RXD A h PMRE d.DLLPs d. In _dll_mo _dll_age l page 2 st items:                                  | A DLLP v<br>Q_ACK_<br>transm<br>nitor-@?                                                 | was ser<br>DLLP w<br>nition sh<br>7406 d<br>104. PC<br>mplian<br>.9#6 S                    | nt<br>vas<br>hould be<br>of P_EP<br>CIE Spec:<br>ice<br>Sent     | specman                     | dut_error                  | 51526   | local_log.log<br>-        |                    | fines/pio_enum<br>suite_top.e/vr_pcie_t                   | test_pm_all.e       | 881853042  | failed      |  |

| _                         | MER Up<br>vr_pcie                                                                                 | dateFC<br>_dll_mo                                                                                 | timer h<br>nitor-@7                                                                      | -<br>as exp<br>7406 с                                                                      | oired In                                                         | specman                     | dut_error                  | 79600   | local_log.log<br>-        |                    | fines/pio_enum<br>suite_top.e/vr_pcie_t                   | test_pl_ltssm_all.e | 1577333793 | failed      |  |

| MINING HT                 |                                                                                                   |                                                                                                   |                                                                                          |                                                                                            |                                                                  |                             |                            |         |                           |                    |                                                           | HTML File           | Ready      |             |  |

## Interoperability Efforts

TL Engineer

Team Lead

**Strategy Managers**

**GPEX** Design IP

Cadence

**VIP**

**Rambus VIP**

(CoverMore)

**Project** Manager

Verification Engineer

Tool R&D Engineer

Tool R&D Engineer

2007 Ram

MAC Engineer

Huge efforts spent to help the customer integrate IP smoothly

# Interoperability Efforts

- Several man-years worth of efforts

- Design IP Development

- VIP Development

- Interoperability efforts

- Tool Licenses

- Methodologies

- Customer approval

#### Rambus and Cadence Collaboration Deliverables

- Design IP

- PCI Express Digital controller, PHY

- Verification IPs

- CoverMore VIP

- Cadence eVC VIP

- ✓ PCI Express eVC

- ✓ Supports e and/or SystemVerilog test benches

- ✓ PCI Express Compliance Management System

- Executable verification plan (vPlan)

- ✓ Test suite to achieve 70% + coverage

- ✓ Rambus specific package for Verification

- ✓ Refinement file for PCI Express vPlan

- Additional test sequences to maximize coverage

Rambus

#### **Summary**

Rambus + Cadence collaboration solves IP Integration challenges

- Independently verified

- Independently created models

- Independently cross-checked

- Tightest integration of Design IP and VIP

- Combined expertise of Rambus and Cadence

- Most automated solution

- Cadence CMS automates verification

- Digital core customizable protocol support