### **Plan to Silicon**

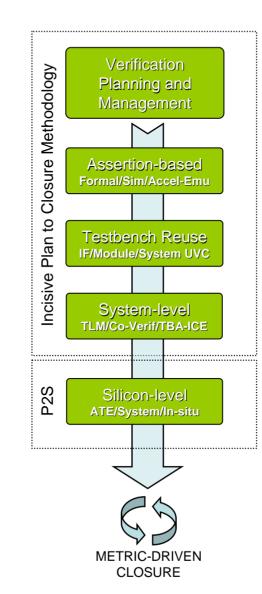

Functional Test Automation using the Incisive platform and Plan to Closure Methodology

Session 1.15 CDNLive! Silicon Valley September 2007 Copyright © 2007 Globetech Solutions

Industry's most complete and reliable flow from design specification to low-risk design closure

c d n

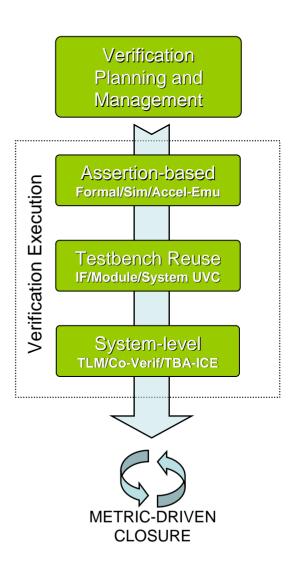

• Addresses:

alobetech

- Verification planning and management

- Assertion-based verification

- Testbench automation and reuse

- Full system verification

- Process-driven flow based on metrics

- Highly-reusable and IP-ready

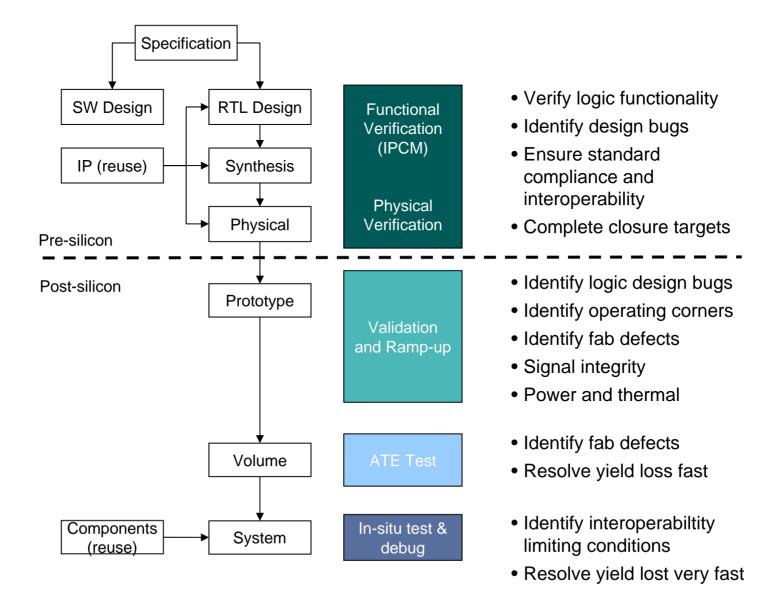

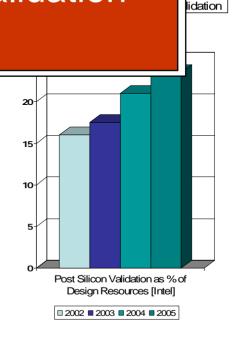

### Validation Overview

- Post-silicon validation cost is rising faster than design cost [Intel, ITC'06]

- Design does not account for all parameters

- Rame Can IPCM be extended to help

- At 65i affect

- address the post-silicon validation challenge?

- Silicon debug is time-critical

- >10% yield loss for 6 wks of production can be >\$100M

- At system, no-trouble-found yield loss thins profit margins

- Requirement to debug in-situ and analyze large data

brt

100%

80%

60%

40%

### From Verification to Test

- Extending verification methodology can help address the post-silicon validation challenge

- Leverage designer knowledge and experience

- Reuse environments and tools

- Know when to look when problems are identified

- Build hardware support to enhance time-to-debug

- Tackle massive unpredictability for TTx

- Looking at verification, post-silicon validation and silicon test from a methodology stand-point:

- All domains need some form of test generation

- All domains need arch/micro micro-arch knowledge

- All domains need coverage metrics

- All domains need some form of failure debug

- Design hooks for one domain can benefit another

Ref: Seva Yerramili, Intel, ITC 2006

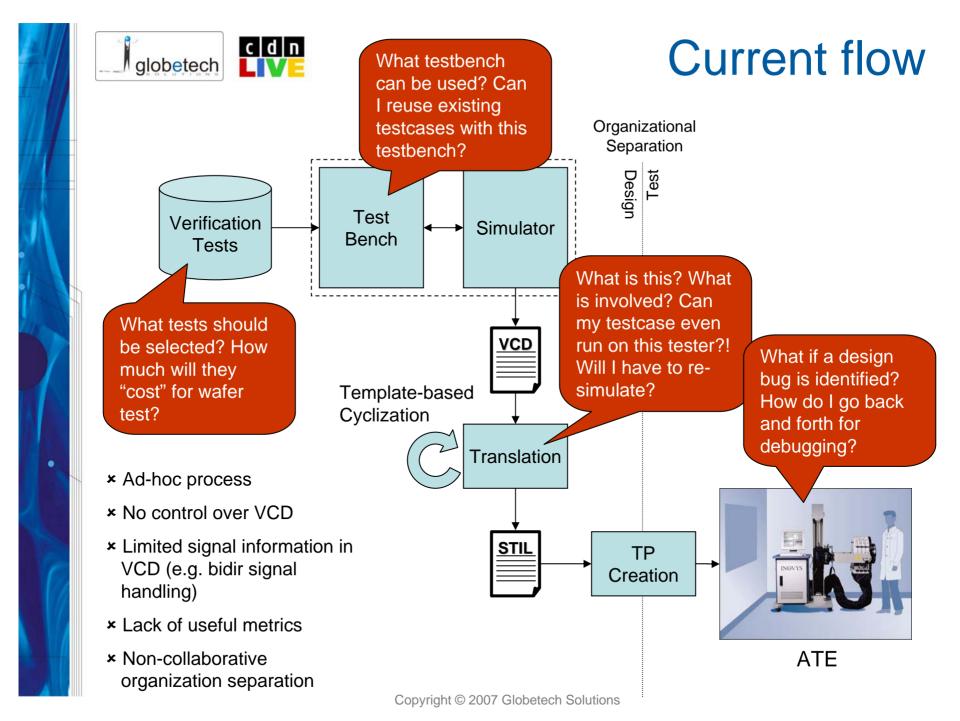

### **5 Distinct Problems**

- How do I select appropriate tests

- How do I reuse testbenches

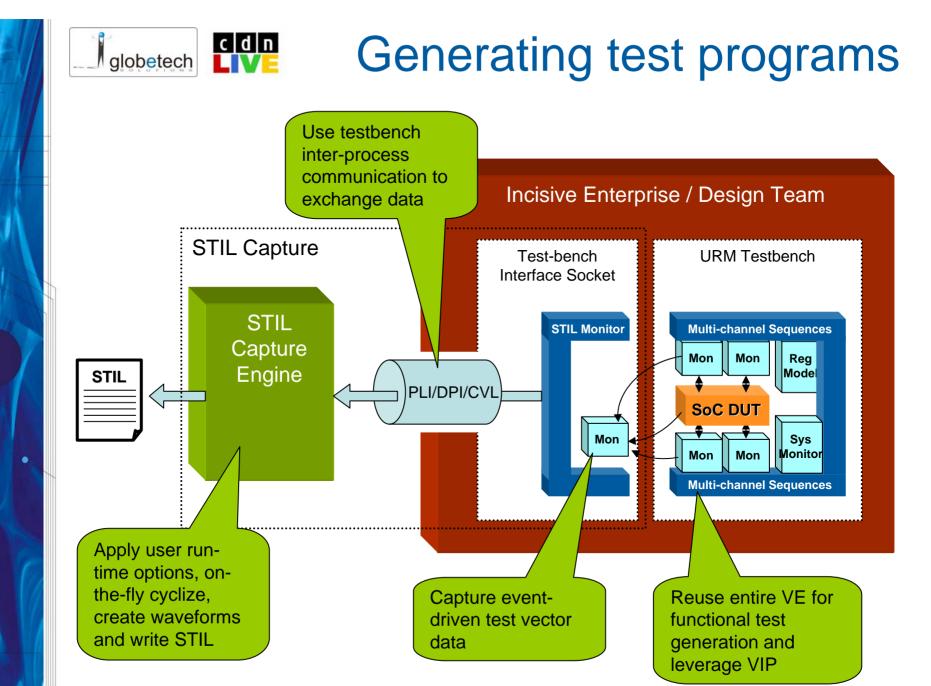

- How do I create working test programs

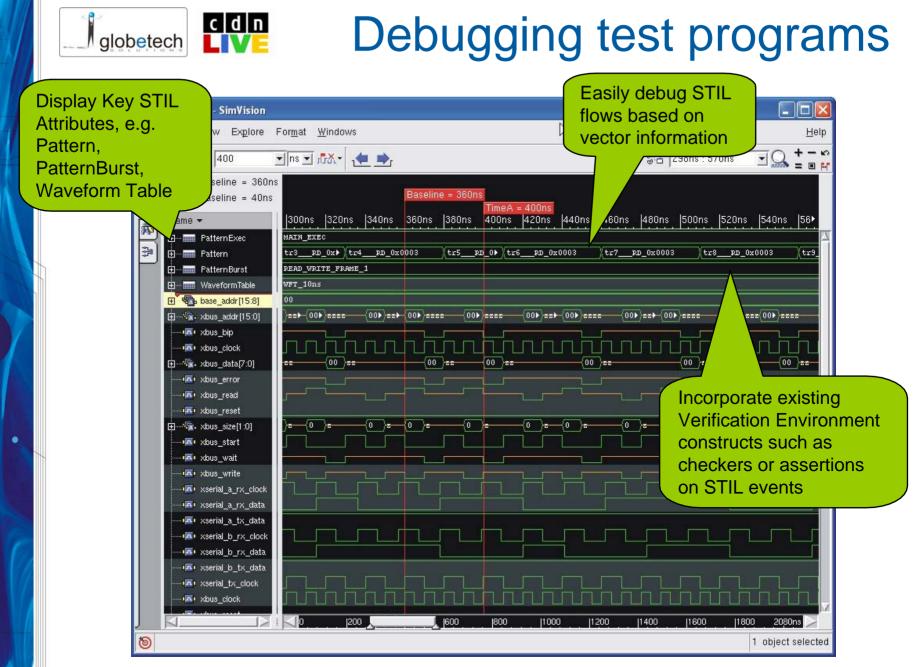

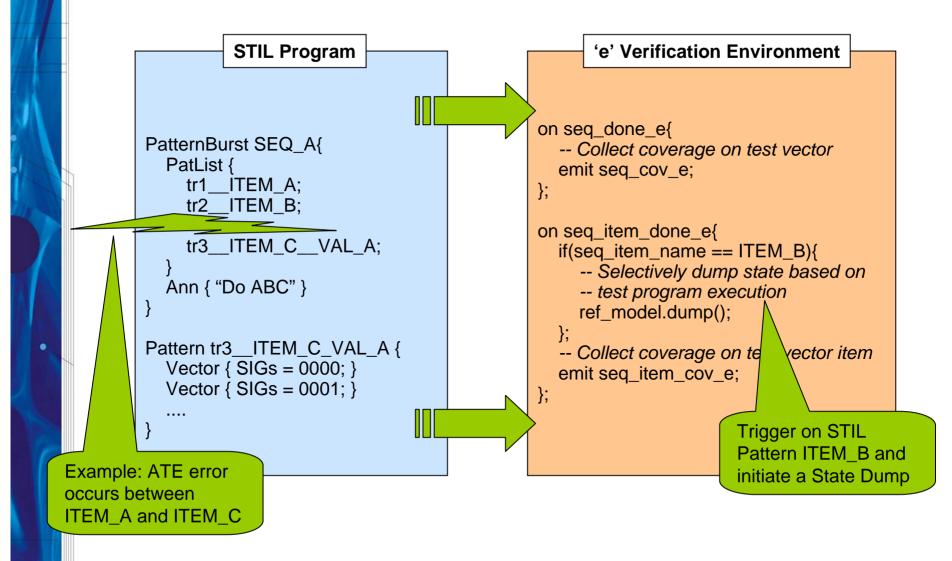

- How do I debug test programs and validate fixes

- How do I manage the validation process

## **Selecting Appropriate Tests**

#### Appropriate for what?

- Functionality

- All round IC exercise

- Interface specific (DDR, PCIe, etc)

#### Design/Verification

- Problem areas where many bugs were found

- Areas were no bugs were found

- Last minute design netlist changes

- Functional coverage matrix (graded)

#### Physical

- Maximum power draw

- Minimum power draw (standby/hibernate)

- Thermal or EMI

- Many others....

#### • Keeping in mind

ATE imposes many constraints on test programs

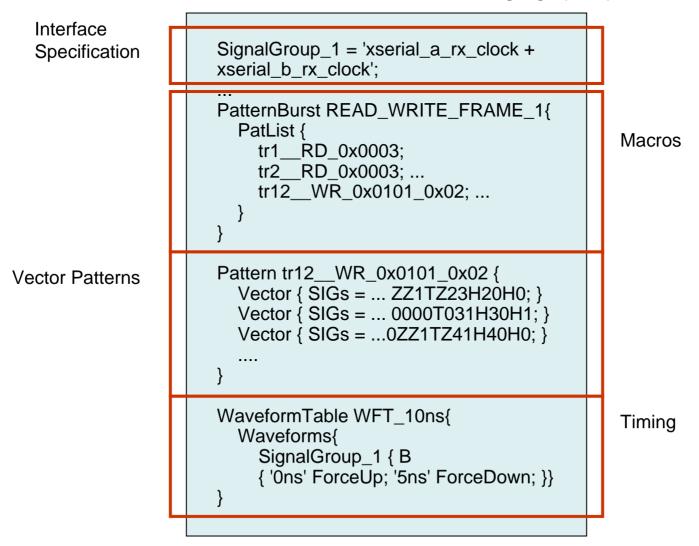

### Looking at a test program

IEEE 1450.1 Standard Test Interface Language (STIL)

### **Functional test metrics**

#### Interfaces

- Number of I/Os

- Types of I/Os (bidir, high-speed, \_oe, etc)

#### • Data

- Number of vectors in set

- Vector depth

#### • Timing

- Cycle duration

- Number of waveform tables

- Number of waveforms

- Number of waveform characters per waveform

#### Semantics

- Importance of vector sets (test coverage, functional coverage, etc)

- Association of data sets with verification history (e.g. failing assertions)

- Transaction grouping

- Other...

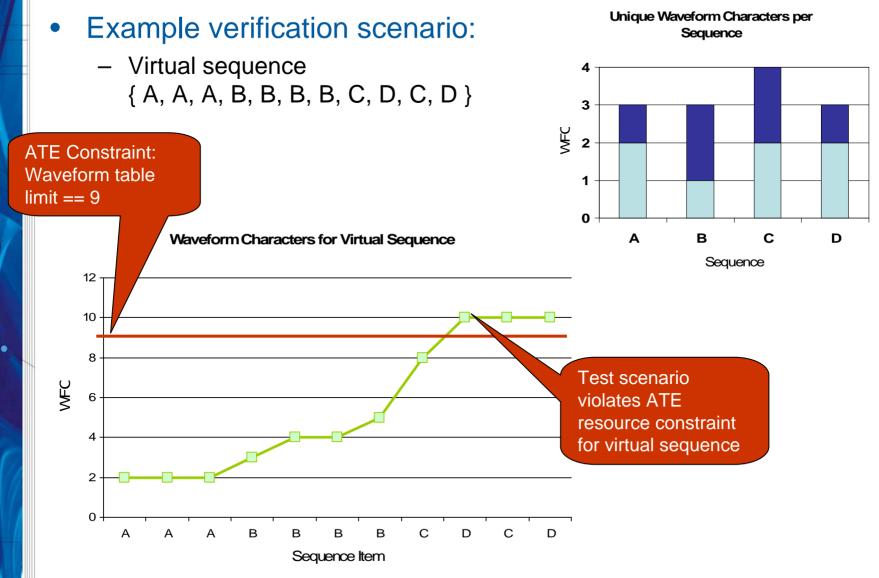

### Analyzing test programs

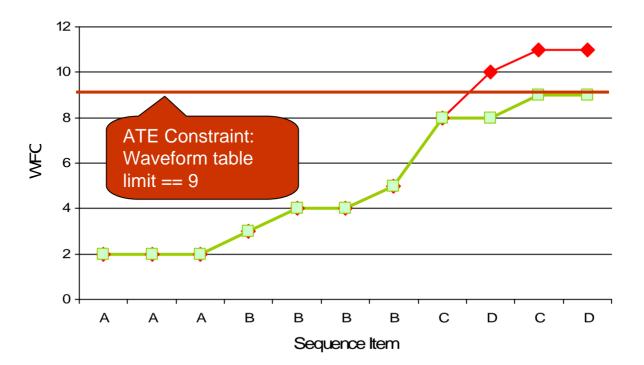

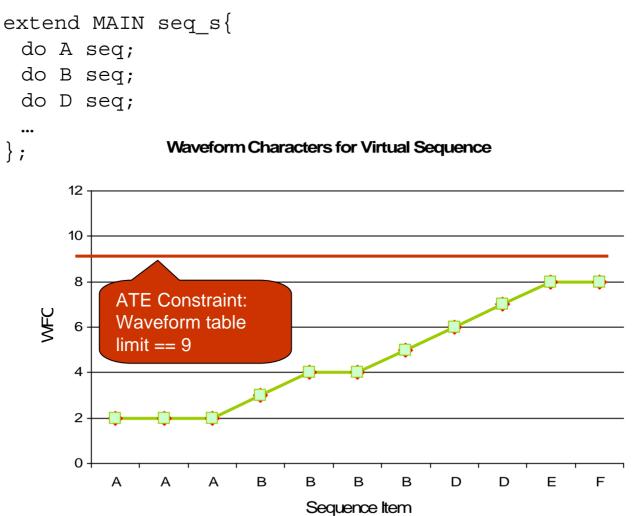

### Fix by Constraint

#### • Control WFC generation by constraint, e.g.:

```

extend C item_s {

keep range in [0..2];

};

```

#### Waveform Characters for Virtual Sequence

### Fix by Test Reordering

#### • After reviewing, decide to skip sequence 'C' altogether:

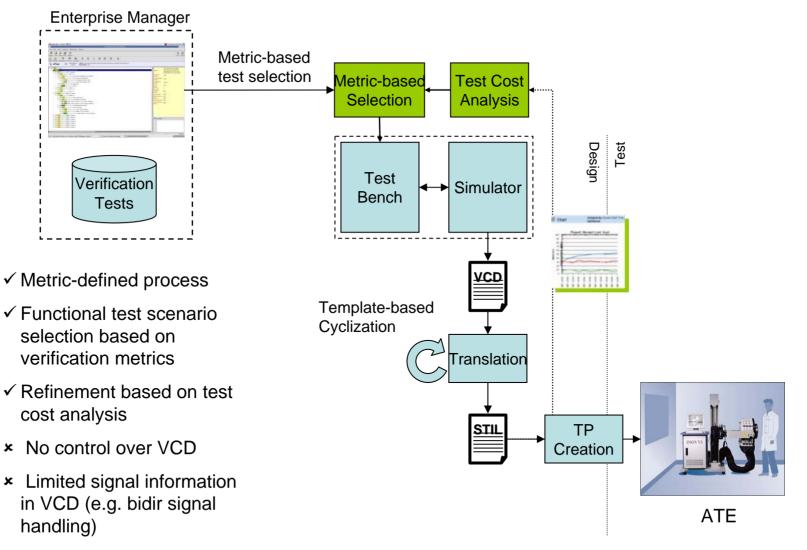

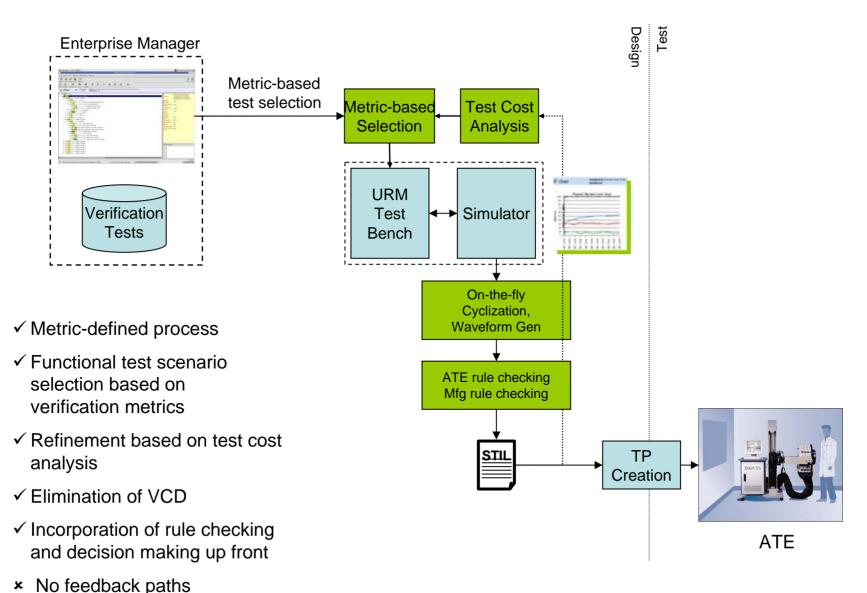

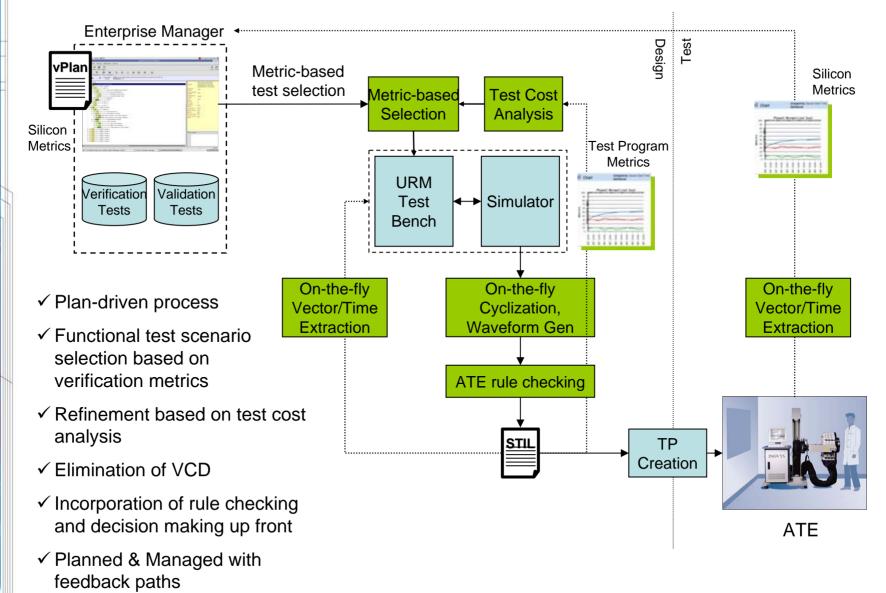

### Extending the current flow

No feedback paths ×

×

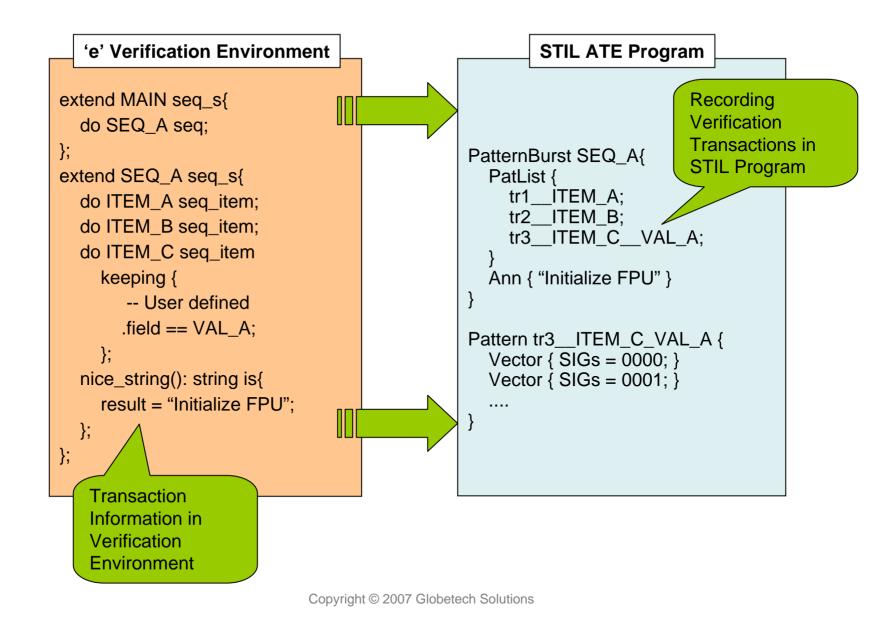

### **Transaction Recording**

### Extending the current flow

### Feeding test data to design

- Debugging post-silicon design problems

- ATE will say:

- Failure at vector # 1249210

- What was the device trying to accomplish at the time?

- What was the state of the device at the time?

- Simulation model

- Real silicon

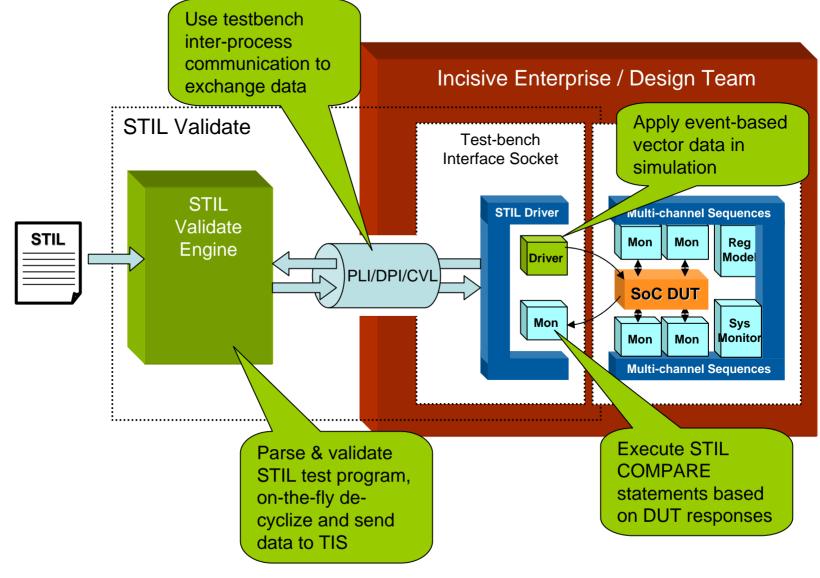

#### • Need a way to incorporate test programs into simulation

- Simulate test programs in URM testbenches for checking and functional coverage collection

- Debug test programs

- Compare simulation data to real silicon data

- Need a way to incorporate metrics into test programs

- Attributes that track progress

- Can be connected with planning and measurement/reporting

### Simulating test programs

### **Test Program Assertions**

### Plan & Manage validation

- Back to validation metrics

- Functional and physical

- Plan to fulfilling metrics

- Early assessment of which design attributes need to be validated in silicon

- Build plan for complete metric-driven post-silicon validation

- Validation test suite

- Test reuse with updated constraints

- New tests that target heterogeneous metrics

- Fault model coverage

- Physical (e.g. CPF power targets)

- Back-annotation of plan with actual results from ATE and system

- Measurements from validation process and experimentation

- Blueprint for plan reuse project-to-project

### Silicon Validation Plan

### **1** Silicon validation

#### **1.1 Functional**

#### **1.1.1 Instruction Functionality**

Code: coverage: STIL\_monitor.instruction\_cov\_e (agent\_name==\*);

#### 1.1.2 I/O

#### 1.1.2.1 PCI Express Interface

Code: coverage: STIL\_monitor.io\_cov.PCIe\_cov.lane\_config Code: coverage: STIL monitor.io cov.PCIe cov.speed config

#### **1.2 Structural**

#### **1.3 Electrical**

1.4 Power

#### **1.5 ATE Environment**

Code: coverage: ATE\_monitor.voltage\_margin Code: coverage: ATE\_monitor.temp\_margin

### Post-silicon validation flow

### Plan to Silicon (P2S)

cdn

globetech

### **Benefits of P2S**

#### Enhanced quality of result

- Plan, do not react

- Anticipate and learn

- Increased design productivity

- Improved specialist integration

- Verification, test, diagnostics, yield

- Reduced support overhead

- Less friction between design for test

- Less black magic

#### • Significant cost-of-test savings

Optimized functional test content targeted at different parts of the postsilicon life-cycle

cadence designer network

# CONNECT: IDEAS

### **CDNLive! 2007 Silicon Valley**