# DDR2 and DDR3 Challenges Dirgha Khatri Micron Technology, Inc. Session # 8.4

9/17/2007

©2006 Micron Technology, Inc. All rights reserved. Products are warranted only to meet Micron's production data sheet specifications. Information, products and/or specifications are subject to change without notice. All information is provided on an "AS IS" basis without warranties of any kind. Dates are estimates only. Drawings not to scale. Micron and the Micron logo are trademarks of Micron Technology, Inc. All other trademarks are the property of their respective owners.

# Outline

- 1. Comparing DDR2 and DDR3

- 1. Tree Topology

- 2. Fly-By Topology

- 3. Data Channel

- 2. Using Allegro PCB SI

- 1. Post-layout analysis using Bus Analysis in Allegro PCB SI

- 2. Timing Budget for DDR2 and DDR3

- 3. Comprehensive simulation in Allegro PCB SI

- 4. S-Parameter Package Model in Allegro PCB SI

- 3. Correlation Lab versus Simulation

- 4. Summary

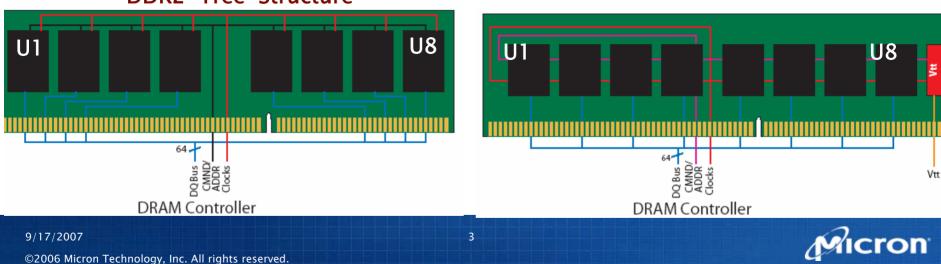

# Topology

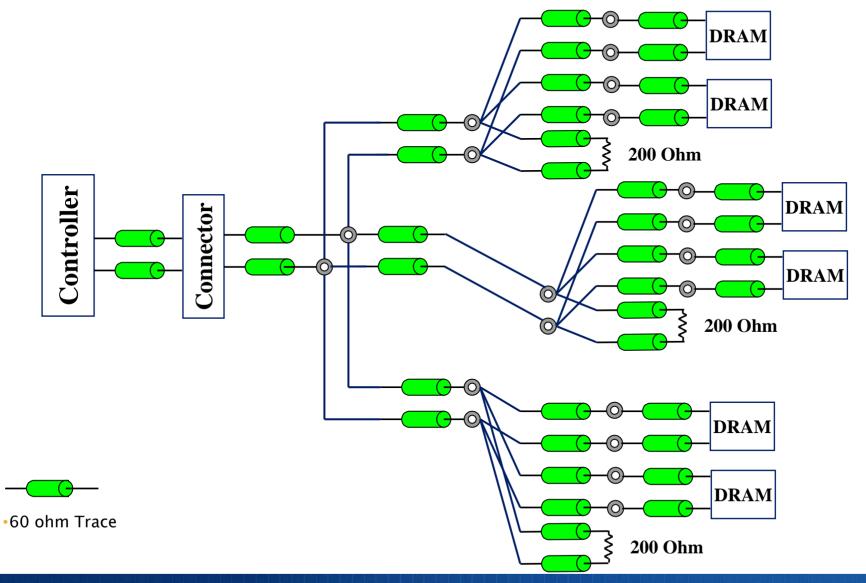

#### • DDR2 memory modules uses tree topology which

- > Increases number of stubs and stub length

- > Signal arrival time is same on each DRAM

- Address/Command/Control has a VTT termination on the system board

- Less data-eye margin

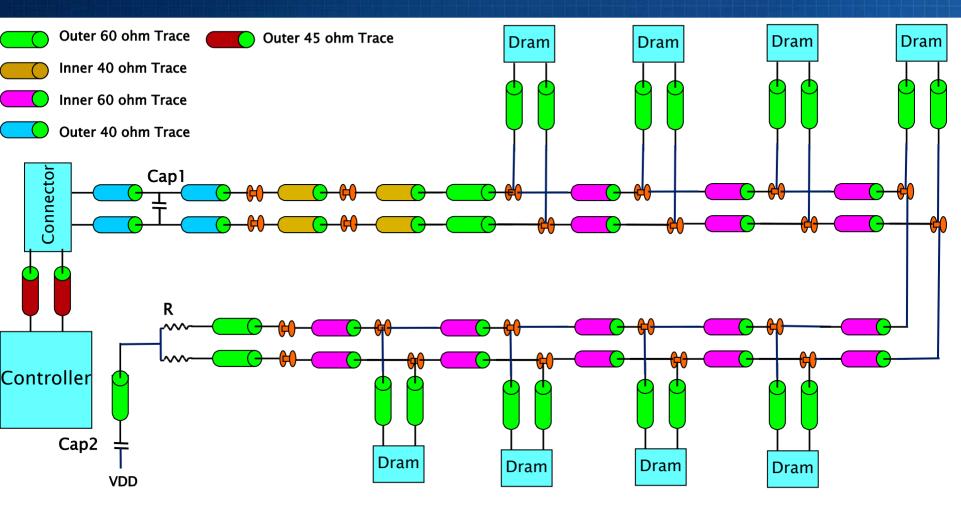

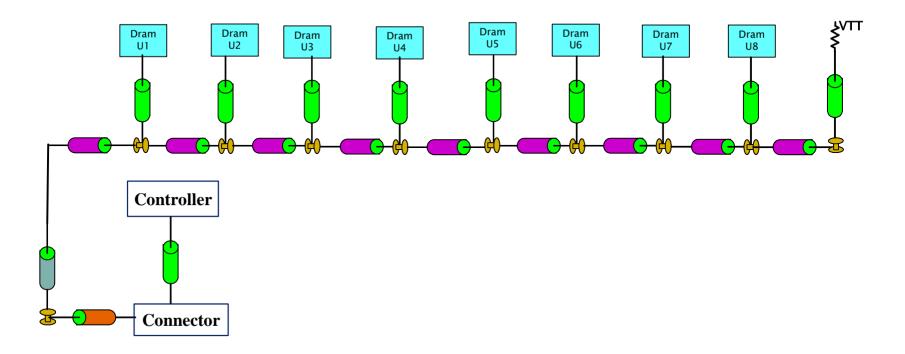

- DDR3 memory modules uses fly-by topology which

- > Reduces number of stubs and stub length

- > Causes interconnect delay skew between clock and strobe at every DRAM on DIMM

- Address/Command/Control has a VTT termination at the far end of the bus on the module

- More bandwidth

#### DDR2 'Tree' Structure

#### DDR3 'Fly-By' Structure

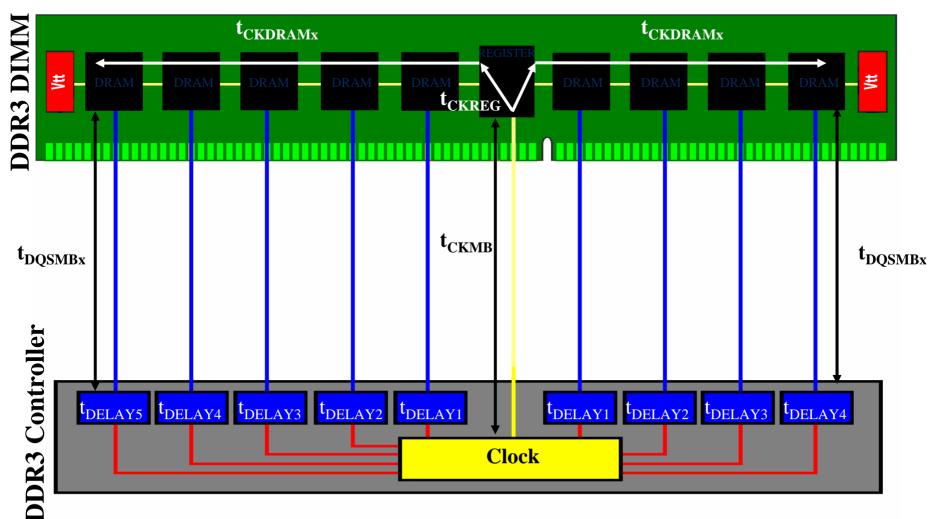

## Write Levelization

$t_{Delayx} + t_{DQSMBx} = t_{CKMB} + t_{CKREG} + t_{CKDRAMx}$

9/17/2007

4

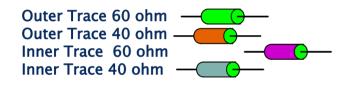

## **Tree Topology**

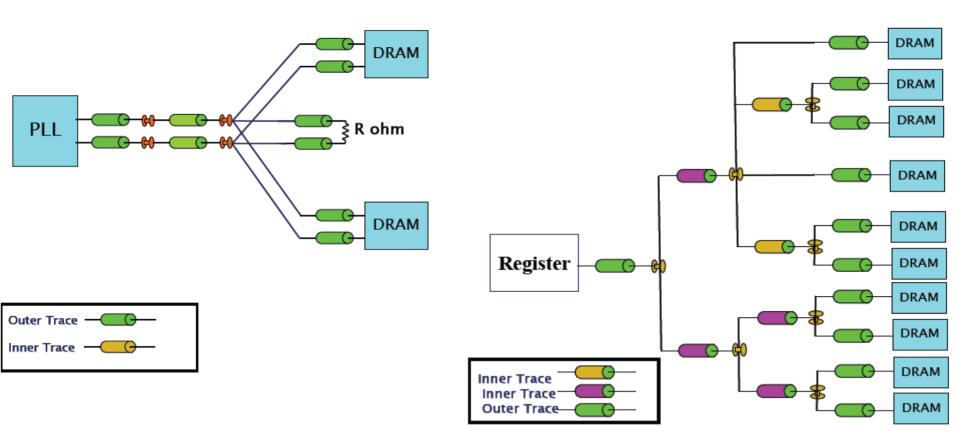

# Fly-by Topology

### **DDR2 UDIMM Clock Topology**

©2006 Micron Technology, Inc. All rights reserved.

# DDR3 UDIMM Fly-by Clock Topology

## **DDR2 UDIMM Address Topology**

©2006 Micron Technology, Inc. All rights reserved.

# DDR3 UDIMM Fly-by Address Topology

• DDR3 UDIMM nets have unloaded and loaded sections on Address/Command/Control topology • This was required to obtain better impedance match in a system

©2006 Micron Technology, Inc. All rights reserved.

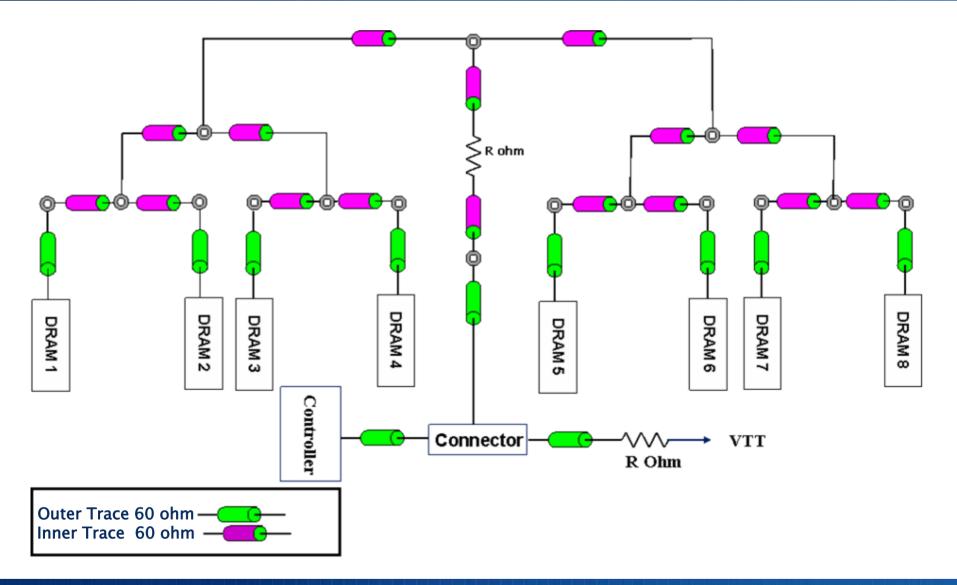

### **DDR2 RDIMM Post Register Nets**

#### **Clock Topology**

#### **Address Topology**

#### Note : All 60 ohm Trace

| 9/17/2007 11                                       | Micron |

|----------------------------------------------------|--------|

| ©2006 Micron Technology, Inc. All rights reserved. | Aucion |

|                                                    |        |

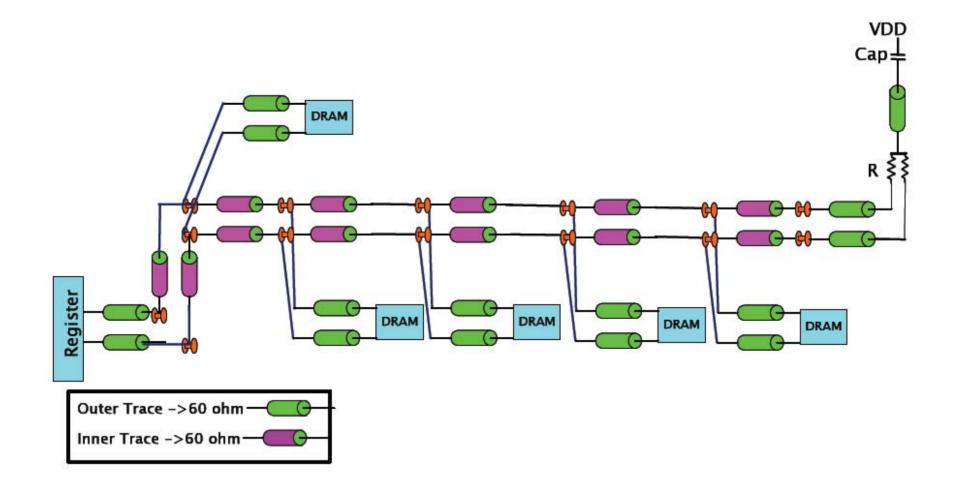

## DDR3 RDIMM Fly-by Clock Topology

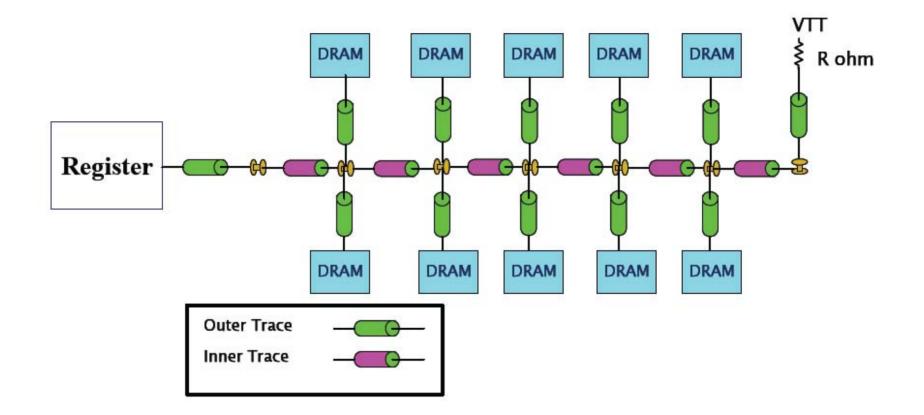

## DDR3 RDIMM Fly-by Address Topology

#### Note : All 60 ohm Trace

9/17/2007

#### Micron

©2006 Micron Technology, Inc. All rights reserved.

#### Improvements to the Data Channel

- The DDR3 data channel can run faster due to enhancements in the DDR3 component

- DDR2 ODT values reflect only:  $50\Omega$ ,  $75\Omega$ ,  $150\Omega$

- DDR3 ODT values include:  $20\Omega$ ,  $30\Omega$ ,  $40\Omega$ ,  $60\Omega$ ,  $120\Omega$

- DDR3 supports dynamic ODT

| DR | SR                | Slot 1    | off         | ff <b>120</b> Ω ODT off |              | 20 <u>0</u>   | na          |

|----|-------------------|-----------|-------------|-------------------------|--------------|---------------|-------------|

| DK | 28                | Slot 2    | off         | ODT off                 | 20 <u>0</u>  | 120 <u>0</u>  | na          |

| SR | DR                | Slot 1    | off         | 120 <u>0</u>            | na           | ODT off       | 20 <u>0</u> |

| ы  | DK .              | DR Slot 2 |             | 20 <u>0</u>             | na           | 1 20 <u>0</u> | ODT off     |

| SR | C D               | Slot 1    | off         | 120 <u>0</u>            | na           | 30 <u>0</u>   | na          |

| ж  | SR Slot 2 off 30Ω |           | 30 <u>0</u> | na                      | 120 <u>0</u> | na            |             |

©2006 Micron Technology, Inc. All rights reserved.

# Bus Setup and Simulation Allegro PCB SI

| 🙀 Create Simulation Bu                                                                                                           | ses     |                          |                                                                 |     | _ 🗆 X |

|----------------------------------------------------------------------------------------------------------------------------------|---------|--------------------------|-----------------------------------------------------------------|-----|-------|

| Buses                                                                                                                            | Add Bus |                          | Delete B                                                        | us  |       |

| DQ_FIRSTBYTE                                                                                                                     |         |                          |                                                                 |     |       |

| _Items not in Bu                                                                                                                 |         | Bus: DQ_FIRS             | TBYTE<br>  Items in                                             | Bus |       |

| Filter:<br>A0<br>A1<br>A2<br>A3<br>A4<br>A5<br>A6<br>A7<br>A8<br>A9<br>A10<br>A11<br>A12<br>A13<br>A14<br>A15<br>BA0<br>RA1<br>◀ |         | <a11<br>A11&gt;</a11<br> | Filter:<br>DQ0<br>DQ1<br>DQ2<br>DQ3<br>DQ4<br>DQ5<br>DQ6<br>DQ7 | *   |       |

| OK                                                                                                                               | Apply   |                          | Cancel                                                          | H   | lelp  |

#### • PCB SI V16.0 allows you to assign models in two different ways 1. Assign by : Model Selector

| 🐉 Signal Bus Setup                                                                                             |                                                                                                    |                  |                            |                  |                      |                    | _ 🗆 × |

|----------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------|------------------|----------------------------|------------------|----------------------|--------------------|-------|

| Select Bus to Setup<br>Bus Name:<br>Bus Direction:<br>Controller Refdes:<br>Switch On:<br>Derating Table File: | MBRD DQ_FIRSTBYTE<br>© UniDirectional © BiDirecti<br>MBRD U1<br>Both Edges<br>ddr3_dq_derating.dat | .onal            |                            | ulation Bus      |                      |                    |       |

| Assign Bus Component E<br>Assign By:                                                                           | Model Select Clocks or St                                                                          |                  | s Xnets to (               |                  | » <br>               |                    |       |

| Component Model                                                                                                |                                                                                                    | Driver           |                            | Active Rece      |                      | Standby Receiver   | _     |

| MT41J128M8HX                                                                                                   |                                                                                                    | V48C_DQ_3        | 34 🔽                       |                  | T120 -               | V48C_DQ_34         |       |

| DDR3_Driver                                                                                                    | DDR3_DRIVER_DDR3_DATA                                                                              | DRIVER_Data_I    | D_1p5X_OD <mark>  -</mark> | DDR3_DRIVER_Dat. | <u>∎_IO_1X</u>  •  D | DR3_DRIVER_Data_1p | .5X • |

|                                                                                                                |                                                                                                    |                  |                            |                  |                      |                    |       |

| Export<br>Import                                                                                               | er Model To Be Assigned:                                                                           | DDR3_DRIVER_Data | _,                         | DDR3_DRIVER_Data |                      | R3_DRIVER_Data_1X  | •     |

| OK                                                                                                             | Apply                                                                                              |                  |                            | Cancel           |                      |                    | Help  |

©2006 Micron Technology, Inc. All rights reserved.

#### 2. Assign by: Component

| 🙀 Signal Bus Setup                                                                                             |                                                                                                                                          |                          |                                                  | _ 🗆 🗙                       |

|----------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------|--------------------------|--------------------------------------------------|-----------------------------|

| Select Bus to Setup<br>Bus Name:<br>Bus Direction:<br>Controller Refdes:<br>Switch On:<br>Derating Table File: | MBRD DQ_FIRSTBYTE<br>O UniDirectional  O BiDirecti<br>MBRD U1<br>Both Edges<br>ddr3_dq_derating.dat<br>Buffer Models Select Clocks or St | onal Assign Bu           | nulation Bus<br>us Stimulus<br>Clocks or Strobes |                             |

| Assign By:                                                                                                     | Model Selector © Component                                                                                                               |                          |                                                  |                             |

| *                                                                                                              | ▼ <b>*</b>                                                                                                                               | *                        | *                                                | *                           |

| Component                                                                                                      | Model Selector                                                                                                                           | Driver                   | Active Receiver                                  | Standby Receivers           |

| MODULE2 U1                                                                                                     | V48C_DQ                                                                                                                                  | ₩48C_DQ_34 -             | V48C_DQ_34_ODT120                                | • V48C_DQ_34 •              |

| MODULE2 U21                                                                                                    | V48C_DQ                                                                                                                                  | V48C_DQ_34 🗸             | V48C_DQ_34 ·                                     | • V48C_DQ_34_ODT30 •        |

| MODULE1 U1                                                                                                     | ₩48C_DQ                                                                                                                                  | ₩48C_DQ_34 💌             | ▼48C_DQ_34_ODT120 •                              | • V48C_DQ_34 •              |

| MODULE1 U21                                                                                                    | V48C_DQ                                                                                                                                  | V48C_DQ_34 -             | V48C_DQ_34                                       | • <u>V48C_DQ_34_ODT30</u> • |

| MBRD U1                                                                                                        | DDR3_DRIVER_DDR3_DATA                                                                                                                    | 3_DRIVER_Data_IO_1p5X_OD | DDR3_DRIVER_Data_IO_1X                           | DDR3_DRIVER_Data_1p5X       |

| Export                                                                                                         | er Model To Be Assigned:                                                                                                                 | DDR3_DRIVER_Data_1X      | DDR3_DRIVER_Data_IO_1X                           | DDR3_DRIVER_Data_1X         |

| Import                                                                                                         |                                                                                                                                          | Assign                   | Assign                                           | Assign                      |

| OK                                                                                                             | Apply                                                                                                                                    |                          | Cancel                                           | Help                        |

|                                                                                                                |                                                                                                                                          |                          |                                                  |                             |

©2006 Micron Technology, Inc. All rights reserved.

#### • Bus is assigned to the selected Clock or Strobe

| 💐 Signal Bus Setup                |                                                                                                                                                                  |

|-----------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Select Bus to Setup               |                                                                                                                                                                  |

| Bus Name:                         | MBRD DQ_FIRSTBYTE Create Simulation Bus                                                                                                                          |

| Bus Direction:                    | O UniDirectional       BiDirectional                                                                                                                             |

| Controller Refdes:                | MBRD U1 Assign Bus Stimulus                                                                                                                                      |

| Switch On:                        | Both Edges                                                                                                                                                       |

| Derating Table File:              | ddr3_dq_derating.dat                                                                                                                                             |

|                                   | Buffer Models Select Clocks or Strobes Assign Bus Xnets to Clocks or Strobes                                                                                     |

|                                   |                                                                                                                                                                  |

|                                   | Unassigned Bus Xnets Assigned Bus Xnets                                                                                                                          |

| List Filters:<br>Export<br>Import | *<br>2dimm_550 DQ0<br>2dimm_550 DQ2<br>2dimm_550 DQ2<br>2dimm_550 DQ3<br>2dimm_550 DQ5<br>2dimm_550 DQ6<br>2dimm_550 DQ6<br>2dimm_550 DQ7<br><all< th=""></all<> |

|                                   |                                                                                                                                                                  |

| ОК                                | Apply Cancel Help                                                                                                                                                |

|                                   |                                                                                                                                                                  |

©2006 Micron Technology, Inc. All rights reserved.

#### • Derating:

| 🙀 Signal Bus Setup                                                                                                        |                                         |                    |                                                 |                     | _ 🗆 X |

|---------------------------------------------------------------------------------------------------------------------------|-----------------------------------------|--------------------|-------------------------------------------------|---------------------|-------|

| Bus Direction: O Un<br>Controller Refdes: U1<br>Switch On: Ris:<br>Derating Table File Iddr<br>Assign Bus Component Buffe | er Models Select Clocks or St:          | onal Assign Bu     | ulation Bus<br>us Stimulus<br>Clocks or Strobes |                     | 1     |

|                                                                                                                           | del Selector O Component                |                    |                                                 |                     | _     |

| Component Model                                                                                                           | * • • • • • • • • • • • • • • • • • • • | * 🔽<br>Driver      | Active Receiver                                 | × Standby Receivers |       |

| MT41J128M8HX                                                                                                              |                                         | V48C_DQ_40_ODT60 • | V48C_DQ_40_ODT60                                | ▼ V48C_DQ_40_ODT60  |       |

| ■Buffer Mo                                                                                                                | odel To Be Assigned:                    | ▼48C_DQ_34         | ₩48C_DQ_34                                      | ▼ ¥48C_DQ_34        |       |

| Export                                                                                                                    | der 10 De Assigned.                     |                    |                                                 |                     |       |

| Import                                                                                                                    |                                         | Assign             | Assign                                          | Assign              |       |

| OK                                                                                                                        | Apply                                   |                    | Cancel                                          | H                   | elp   |

#### DDR2 Derating table from Micron Data sheet

1Gł

#### Table 33: DDR2-667/DDR2-800/DDR2-1066 <sup>t</sup>DS, <sup>t</sup>DH Derating Values v All units are shown in picoseconds

|                |                                                                              | DQS, DQS# Differential Slew Rate |          |                     |          |                      |          |                         |                 |                           |                 |                     |

|----------------|------------------------------------------------------------------------------|----------------------------------|----------|---------------------|----------|----------------------|----------|-------------------------|-----------------|---------------------------|-----------------|---------------------|

| DQ<br>Slew     | 2.8 V/ns                                                                     |                                  | 2.4      | 2.4 V/ns            |          | 2.0 V/ns             |          | V/ns                    | 1.6 V/ns        |                           | 1.4 V/ns        |                     |

| Rate<br>(V/ns) | ${}^{t}\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!$ | $^{\Delta}_{\text{DH}}$          | $^{t}DS$ | <sup>∆</sup><br>tOH | $^{t}DS$ | $^{\rm L}{}^{\rm D}$ | $^{t}DS$ | $^{\Delta}_{\text{DH}}$ | <sup>د</sup> DS | ${}^{\Delta}_{\text{DH}}$ | <sup>ئ</sup> DS | <sup>∆</sup><br>tDH |

| 2.0            | 100                                                                          | 63                               | 100      | 63                  | 100      | 63                   | 112      | 75                      | 124             | 87                        | 136             | 99                  |

| 1.5            | 67                                                                           | 42                               | 67       | 42                  | 67       | 42                   | 79       | 54                      | 91              | 66                        | 103             | 78                  |

| 1.0            | 0                                                                            | 0                                | 0        | 0                   | 0        | 0                    | 12       | 12                      | 24              | 24                        | 36<br>31        | 36                  |

| 0.9            | -5                                                                           | -14                              | -5       | -14                 | -5       | -14                  | 7        | -2                      | 19              | 10                        | 51              | 22                  |

#### •CSV format to read into Allegro PCB SI

# Derating table for DDR2 DQ 667/800 DQS\_SLEW,0.8,1.0,1.2,1.4,1.6,1.8,2.0,2.4,2.8 DATA\_SLEW,0.4,0.5,0.6,0.7,0.8,0.9,1.0,1.5,2.0 SETUP\_DERATING\_TABLE -28,12,38,50,59,67,72,139,172 -40,0,26,38,47,55,60,127,160 -52,12,14,26,35,43,48,115,148 -64,-24,2,14,23,31,36,103,136 HOLD\_DERATING\_TABLE -116,-53,-11,18,41,58,72,114,135 -128,-65,-23,6,29,46,60,102,123 -140,-77,-35,-6,17,34,48,90,111 -152,-89,-47,-18,5,22,36,78,99

©2006 Micron Technology, Inc. All rights reserved.

# **DDR2 RDIMM**

#### **Post Register Timing Budget**

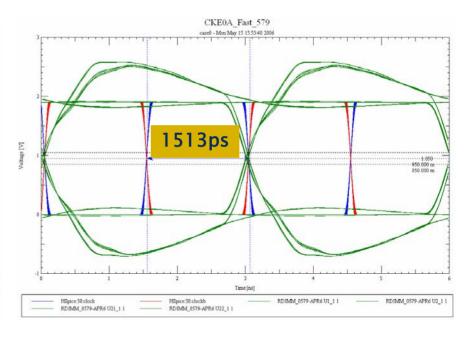

#### DDR2 Post Register Simulation Hspice Simulation

#### ODT1B Slow 579 rasel - Mon May 15 15 23 59 2006 2113ps 1.050 850.000 m [v] oltage [V] 650 000 m Time [ns] HSpice 46 clock HSpice-Miclockh RDIMM 0579-APR10103.1 RDIMM 0579-APR101141 RDIMM\_0579-APR10 U19 1 RDIMM\_0579-APR10 U20 1 RDIMM 0579-APR10 US RDIMM 0579-APR 10 U18 1

Slow Corner

#### **Fast Corner**

9/17/2007 ©2006 Micron Technology, Inc. All rights reserved.

# **Timing Budget for DDR2 RDIMM**

Register clock to output is determined from the Simulation

Helps in getting more accurate timing budget

• Tlsim can also be used to come up with the Timing Budget

| Timing Budget                        |           |           |          |                                        |  |  |  |

|--------------------------------------|-----------|-----------|----------|----------------------------------------|--|--|--|

| Description                          | Symbol    | Setup(ps) | Hold(ps) |                                        |  |  |  |

| Clock Period                         | tCLK      | 3000      | N/A      |                                        |  |  |  |

| Measured Delay: Clock to Actual Load | tPD       | -2113     | 1513     | Reg_Clk at Vref to Receiver at AC / DC |  |  |  |

| Simultaneous Switching Adder         | tSS       | -200      | N/A      | Register Spec                          |  |  |  |

| *Cross Talk Adder                    | tXTALK    | -50       | -50      | Estimated for non-XTALK SIMM           |  |  |  |

| Intersymbol Interference             | tISI      | N/A       | N/A      | Included in tPD                        |  |  |  |

| Clock Skew                           | tSKEW     | -150      | -130     | PLL jitter/skew + PCB clk skew         |  |  |  |

| Register Clock Shift                 | tREG      | -100      | -100     | Register clock input skew              |  |  |  |

| DRAM Setup/Hold (derating values)    | tISb/tIHb | -200      | -275     | DRAM Spec @ ac/dc thresholds           |  |  |  |

| Derating                             |           | -100      | -94      |                                        |  |  |  |

| * Register Clock Offset              |           | 0         | 0        | As needed to help setup or hold        |  |  |  |

| Margin (worst case corners)          | tM        | 87        | 864      | Unit: ps                               |  |  |  |

# DDR3 RDIMM

#### **Post Register Timing Budget**

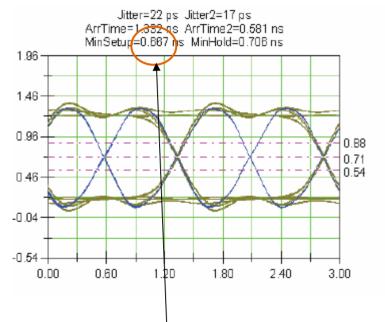

#### **DDR3 Post Register Simulation**

2.04

1.54

1.D4

0.54

0.04

-0.46

0.00

0.60

#### **Address Net in Slow Corner**

#### **Control Net in Fast Corner**

0.98

0.79

0.62

3.00

Jitter=28 ps\_Jitter2=13 ps

ArrTime=0.817 ns. ArrTime2=0.118 os

MinSetup=0.756 ns MinHold=0.860 ns

Minimum Setup Region

Minimum Hold Region

1 ÅD

2.40

1.20

#### Note: Used proprietary Micron tools to plot the data from Allegro PCB SI

26

# **Timing Budget for DDR3 RDIMM**

| Timing Budget at 667MHz - Clock at 50%                                             | /<br>0    |          |

|------------------------------------------------------------------------------------|-----------|----------|

|                                                                                    | Setup(ps) | Hold(ps) |

| Measurement                                                                        | 667       | 660      |

| DRAM setup/hold @ 667MHz Clock                                                     | 50        | 125      |

| Timing offset for VREF error (30 mV) based on min. slew rate<br>(30mv / 2.40 v/ns) | 13        |          |

| Timing offset for VREF error (30 mV) based on min. slew rate<br>(30mv / 3.36 v/ns) |           | 9        |

| DRAM derating                                                                      | 88        | 50       |

| tjit(hper) half period jitter from register                                        | 50        | 50       |

| tQSK1 for Register (includes SSO for inverted outputs)                             | 200       | 100      |

| xtalk                                                                              | 16        | 16       |

| Margin available for Clock placement error (at 50% point)                          | 250       | 310      |

# Comprehensive Simulation

### **Crosstalk Report in Allegro PCB SI**

| 🙀 Analysis Report Generator (case3)                             |                                       |                   |                          |           |                            |            |                                         |                                         |           |

|-----------------------------------------------------------------|---------------------------------------|-------------------|--------------------------|-----------|----------------------------|------------|-----------------------------------------|-----------------------------------------|-----------|

| Standard Report Custom Report                                   |                                       |                   |                          |           |                            |            |                                         |                                         |           |

| Case Selection                                                  |                                       |                   |                          |           |                            |            |                                         |                                         |           |

| Current Case : case3 : case2 + unknown change in 'C:\Cadence\SP |                                       |                   |                          |           |                            |            |                                         |                                         |           |

|                                                                 | ▫੶੶੶੶੶                                |                   |                          |           |                            |            |                                         |                                         |           |

| Report Types                                                    |                                       |                   |                          |           |                            |            |                                         |                                         |           |

| 🔽 🗖 Reflection Summary 🗖 Parasitics 👘 Segment Crosstal          |                                       |                   |                          |           |                            |            |                                         |                                         |           |

| 🗌 🗖 Delay 🦳 SSN 🔽 Crosstalk Summar                              | у                                     | ########          |                          |           |                            |            |                                         | ############                            |           |

| 🗖 Ringing 🦳 SDF Wire Delay 🗖 Crosstalk Detaile                  | ed                                    | #                 |                          | PCB       | SI XL                      |            |                                         |                                         |           |

| 🗖 Single Net EMI                                                |                                       | #                 | 15.7                     | s039      | (v15-7-42B[1/5/2           | 007]       |                                         |                                         |           |

|                                                                 |                                       | #<br>#            | (c)                      | Convright | 1998-2004 Cade             | nce Design | Systems Inc.                            |                                         |           |

| Fast/Typical/Slow Mode<br>Fast Vypical Slow Fast/Slow Slow/Fas  | +                                     | #                 | (0)                      | oopyngin  | 1000 2004 Oddel            | ice Design | Oysterns inc.                           |                                         |           |

| rast   Fightan   Sidw   rast/Sidw   Sidw/ras                    | ۰ــــــــــــــــــــــــــــــــــــ | #                 | Report:                  |           | Crosstalk Sumn             |            | Sorted By                               | Worst Case                              | Crosstalk |

| Primary Net                                                     |                                       | #                 | Tue                      | Apr       | 17 22:5                    |            | )7<br> ######################           | ,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,, |           |

| Net Selection: All Selected Nets                                |                                       | *****             |                          |           |                            | *****      |                                         | *****                                   |           |

| Driver Selection: Fastest Driver                                |                                       |                   |                          |           |                            |            |                                         |                                         |           |

| Aggressor                                                       |                                       | **********<br>All | Neighbors                |           |                            | FTSMod     | ·*************************************  | k                                       |           |

| Switch Mode: Odd                                                |                                       |                   |                          |           |                            |            | e)<br>********************************* | *                                       |           |

| Net Selection:                                                  |                                       | Victim            | XNet                     | Victim    | Drvr                       |            | HSOddXta HSEve                          | enXtaLSOddXtalLSEvenX                   | (talk     |

| Driver Selection: All/Group Neighbors                           |                                       |                   | 2 0550AA 1               |           | 0550AA 1 U7                | <br>M11    | 80.82 NA                                | 79.57 NA                                |           |

| Each Neighbor                                                   |                                       |                   | 2 0550AA_1<br>2 0550AA 1 |           | 0550AA_1 U7                | K11        | 72.43 NA                                | 69.93 NA                                |           |

| Reflection Data Simulation                                      |                                       |                   | 2 0550AA_1               |           | 0550AA_1 U7                | F2         | 65.76 NA                                | 62.56 NA                                |           |

| Type: 🖲 Reflection Measurement:                                 |                                       |                   | 2 0550AA_1               |           | 0550AA_1 U7                | G2         | 65.14 NA                                | 62.23 NA                                |           |

| 🔿 Comprehensive Odd 🛛 💿 Pulse                                   |                                       |                   | 2 0550AA_1               |           | 0550AA_1 U7                | M1         | 57.26 NA                                | 53.51 NA                                |           |

| C Comprehensive Even C Rise/Fall                                |                                       |                   | 2 0550AA_1               |           | 0550AA_1 U7                | C2         | 51.38 NA                                | 49.29 NA                                |           |

|                                                                 |                                       |                   | 2 0550AA_1<br>2 0550AA 1 |           | 0550AA_1 U7<br>0550AA 1 U7 | M10<br>J11 | 50.14 NA<br>48.79 NA                    | 48.21 NA<br>47.9 NA                     |           |

| Comprehensive Static Constant Stimulus Assign                   | a                                     |                   | 2 0550AA_1<br>2 0550AA 1 |           | 0550AA_1 U7                | L1         | 48.45 NA                                | 47.9 NA<br>45.77 NA                     |           |

| 🗌 🔽 Use Timing Windows 🔲 Save Circuit Files 🔽 Save Waveforms    |                                       |                   | 2 0550AA 1               |           | 0550AA 1 U7                | C10        | 47.6 NA                                 | 45.28 NA                                |           |

| Consta Press                                                    |                                       |                   | 2 0550AA 1               |           | 0550AA 1 U7                | N1         | 46.96 NA                                | 44.98 NA                                |           |

| Create Report                                                   |                                       |                   | 2 0550AA_1               | A5A       | 0550AA_1 U7                | D2         | 42.43 NA                                | 40.44 NA                                |           |

|                                                                 |                                       |                   | 2 0550AA_1               | A1A       | 0550AA_1 U7                | F1         | 39.07 NA                                | 37.54 NA                                |           |

| OK Cancel Preferences                                           | Help                                  |                   |                          |           |                            |            |                                         |                                         |           |

## Crosstalk in PCB SI V. 16.0

#### Comprehensive Bus Simulation

| 🙀 Analysis Bus Simulation 📃 🔲 🗙                                      |

|----------------------------------------------------------------------|

| Case Selection<br>Current Case: case5 : Default Settings             |

| Bus To Simulate<br>Bus Name: DATA_BUS  Bus Setup Assign Bus Stimulus |

| Fast/Typical/Slow Mode<br>Fast Typical Slow Fast/Slow Slow/Fast      |

| Receiver Selection<br>All Receivers                                  |

| Simulation Type<br>Reflection Comprehensive                          |

| Simulation Output<br>Show Report Show Waveform Save Circuit Files    |

| Simulate       OK     Cancel       Preferences                       |

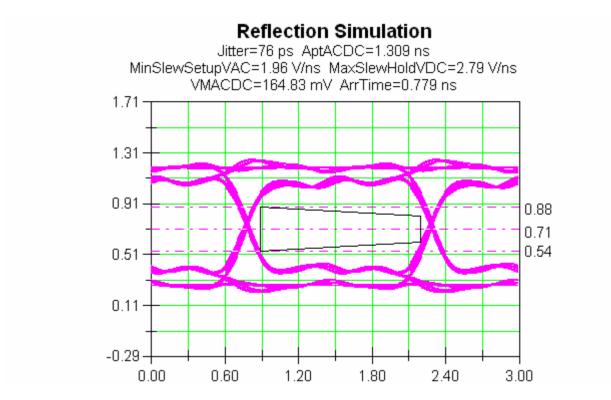

#### **Reflection Simulation in DDR3**

#### Note: Used proprietary Micron tools to plot the data from Allegro PCB SI

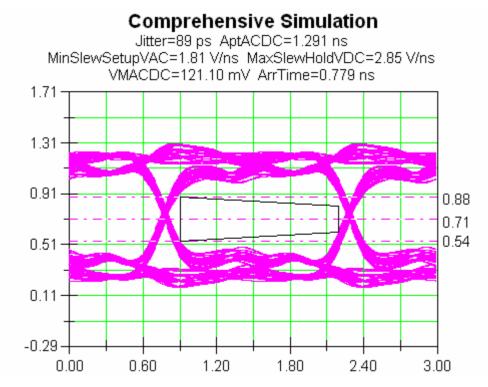

## **Comprehensive Simulation in DDR3**

#### •As an Example following settings were used to run Comprehensive Simulation:

- Geometry Window = 40 mil

- Min. Coupled Length = 50 mil

- Neighbor Capacitance = 0.01 pF

#### Note: Used proprietary Micron tools to plot the data from Allegro PCB SI

©2006 Micron Technology, Inc. All rights reserved.

# S-Parameter Package Model

#### In Allegro PCB SI

### **S**-Parameter

- Scattering Parameters are normally referred as S– Parameters.

- Relates to a traveling waves that are scattered or reflected when an n-port network is inserted into a transmission line.

- S-Parameter models are frequency domain and they describe the behavior of a set of ports at different frequencies.

### S-parameter in Allegro PCB SI

#### • PCB SI V. 16.0 has:

- DC Extrapolation Options

- Causality

- Passivity Check

| 🚧 Analysis Preferences                                                                                    |           |

|-----------------------------------------------------------------------------------------------------------|-----------|

|                                                                                                           | imulation |

| Transient Simulation Preferences                                                                          |           |

| Transient Simulation Method Convolution                                                                   | •         |

| DC Extrapolation Method Default Default                                                                   |           |

| <ul> <li>Enforce Impulse Response Causality MagPhase<br/>Realmag<br/>SmithChart<br/>FirstPoint</li> </ul> |           |

|                                                                                                           |           |

|                                                                                                           |           |

|                                                                                                           |           |

|                                                                                                           |           |

|                                                                                                           |           |

|                                                                                                           |           |

|                                                                                                           |           |

|                                                                                                           |           |

|                                                                                                           |           |

| OK Cancel                                                                                                 | Help      |

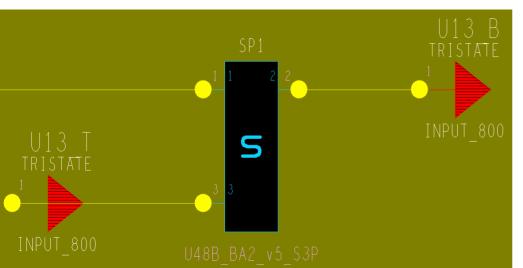

## Using Allegro PCB SI GXL

- Tlsim Engine is used for simulation.

- The converted .dml file from

a touchstone file is shown

here as black box with letter

" S " in Sigxp .

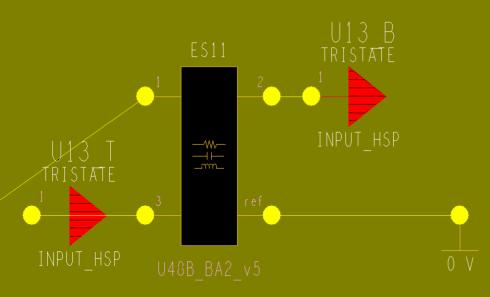

## Using Allegro PCB SI XL

- Hspice Engine is used for Simulation

- The converted .dml file from a touchstone file is shown here as black box in Sigxp

9/17/2007 ©2006 Micron Technology, Inc. All rights reserved.

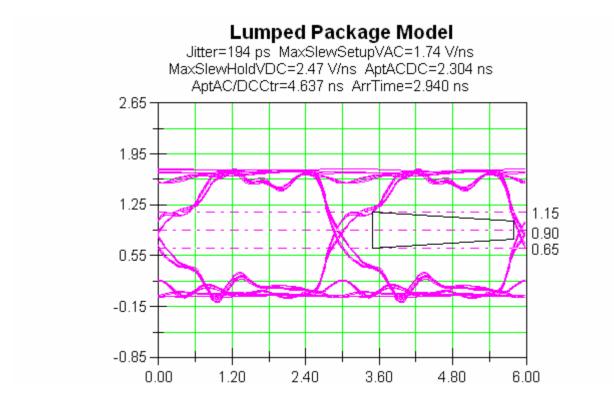

#### Simulation With Lumped Package Model

#### Note: Used proprietary Micron tools to plot the data from Allegro PCB SI

©2006 Micron Technology, Inc. All rights reserved.

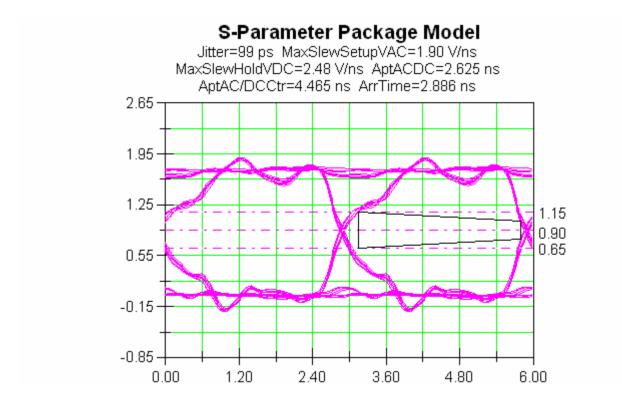

#### Simulation With S-Parameter Package Model

#### Note: Used proprietary Micron tools to plot the data from Allegro PCB SI

©2006 Micron Technology, Inc. All rights reserved.

# Correlation

#### Lab versus Simulation

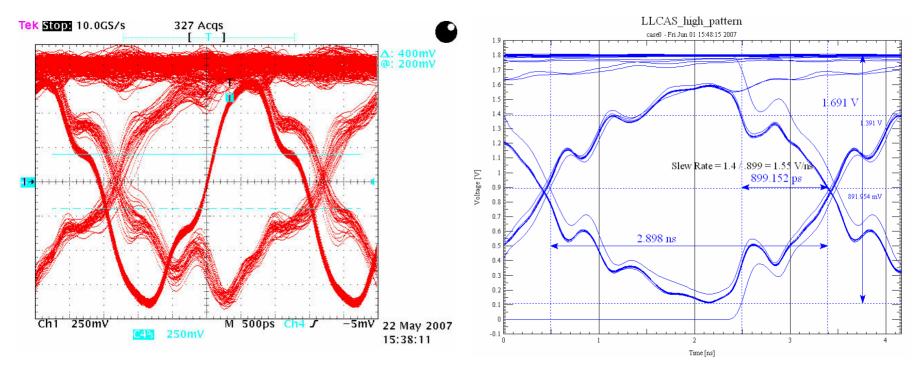

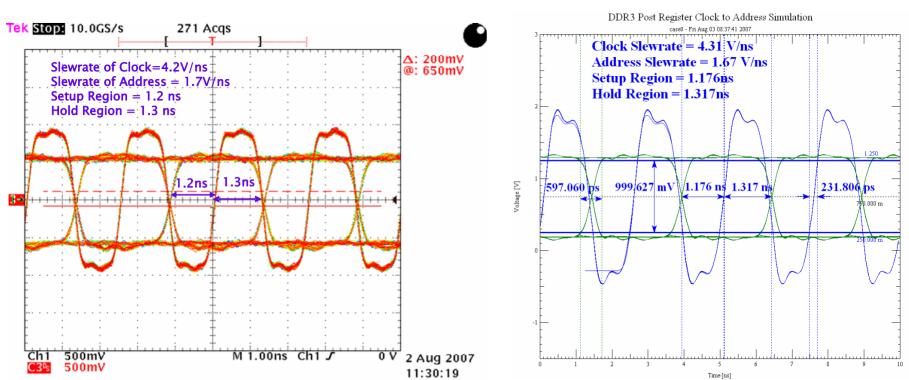

# **DDR2 RDIMM System Verification**

# Lab Measurements versus Simulation Correlation on Address Net in a RDIMM DDR2 Card .

#### Lab Measurements

#### Simulation (Uncoupled)

9/17/2007 ©2006 Micron Technology, Inc. All rights reserved.

# **DDR3 RDIMM System Verification**

Simulation (Uncoupled)

# Lab Measurements versus simulation correlation on Address Net in a RDIMM DDR3 Card.

#### Lab Measurements

# Summary

- The challenges in designing with

- DDR2 reside in signal integrity

- DDR3 reside in timing

- Due to Tree Topology DDR2 signals arrive at the same time in every DRAM even though it has less bandwidth

- Due to DDR3 fly-by topology, timing skews exist from DRAM-to-DRAM

- therefore it is more challenging for the DDR3 controller to match timing even though it has a larger bandwidth

- Allegro PCB SI

- Can be used to design DDR3 with timing issues

- Following enhancements in 16.0 make it easy to get siliconaccurate timing data

- Comprehensive Simulation

- Slewrate derating

- Ease of use improvements with Bus Setup

cadence designer network

# CONNECT: IDEAS

#### **CDNLive! 2007 Silicon Valley**