cādence"

### Modeling and Analysis Methodologies of Complex Digital Systems-in-Package Designs

Zhen Mu

- Design Challenges of System in Package (SiP)

- Modeling and analysis solutions

- Co-Design methodologies

- SI and PI analysis

- Design Challenges of System in Package (SiP)

- Modeling and analysis solutions

- Co-Design methodologies

- SI and PI analysis

- SiP

- Single package that combines all of the electronic components (digital ICs, analog ICs, RF ICs, passive components or other elements) needed to provide a system or sub-system.

Courtesy of Philips

#### **Die stacking**

#### Package-on-package

cādence

© 2007 Cadence Design Systems, Inc. All rights reserved worldwide. 5

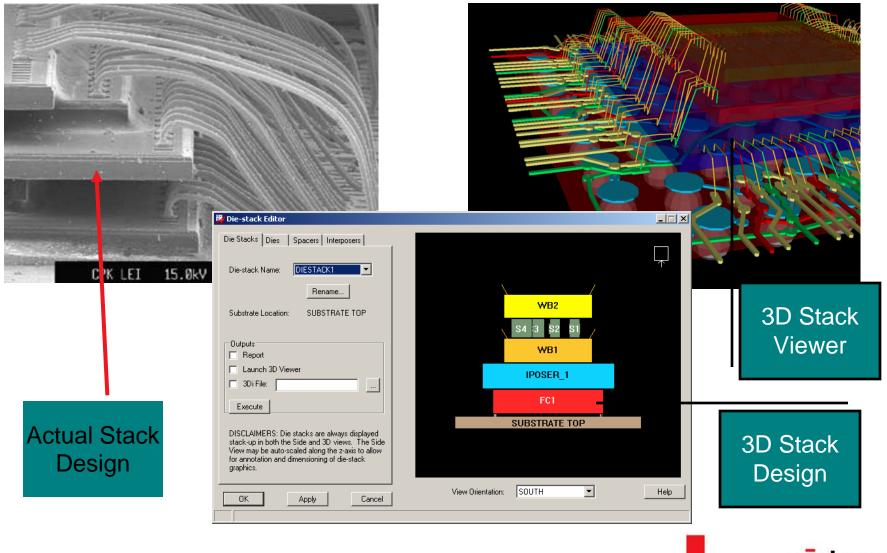

### Complex die stack design

© 2007 Cadence Design Systems, Inc. All rights reserved worldwide.

6

- Design Challenges of System in Package (SiP)

- Modeling and analysis solutions

- Co-Design methodologies

- SI and PI analysis

### Modeling and analysis challenges

- Optimization requires design automation

- Recongnicing the differences between SiP design and classic single package and PCB designs

- Issues

- Multiple stacked dies are placed vertically or horizontally

- Connection between multiple dies are realized by wirebonding, interposer, interconnect, or flip-chip technology

- IC design needs to consider package design, while package design needs to consider IC requirements

- How to make die information available to package designers, and how to pass package models back to IO designers to simulate entire signal path

- Data passing and property mapping

### Modeling and analysis challenges (cont')

- Fundamental requirements for SiP tools

- An environment with IC/package/board co-design and cosimulation capabilities

- To provide engineers with Signal Integrity (SI) and Power Integrity (PI) solutions

- Concurrent pre-route analysis and post-route verification

# Co-design methodologies in high-speed design

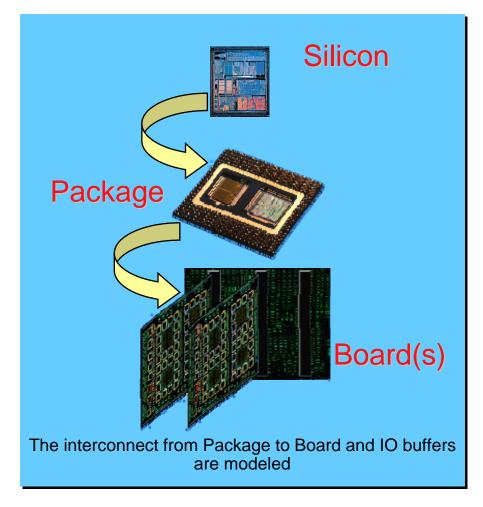

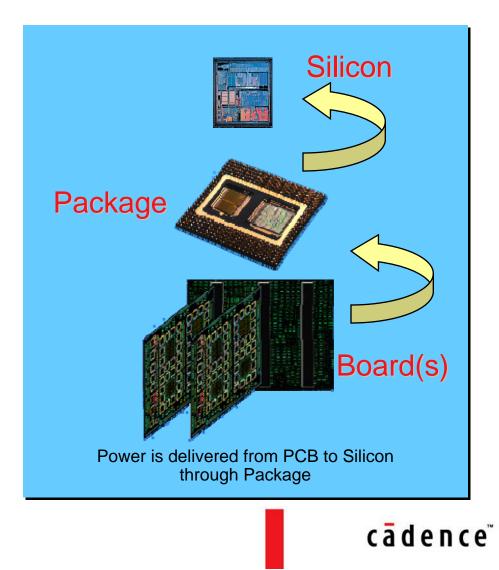

- Problem1: Signal path from silicon to board through package

- Reflections, xtalk, timing

## Co-design methodologies in high-speed design (cont')

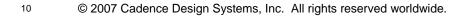

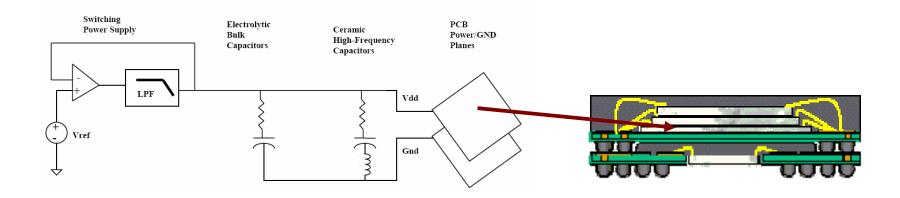

Problem 2: Power delivery path from board to silicon through package

11 © 2007 Cadence Design Systems, Inc. All rights reserved worldwide.

## Co-design methodologies in high-speed design (cont')

• Problem 3: Effects between signal and power supply

## Co-design methodologies in high-speed design (cont')

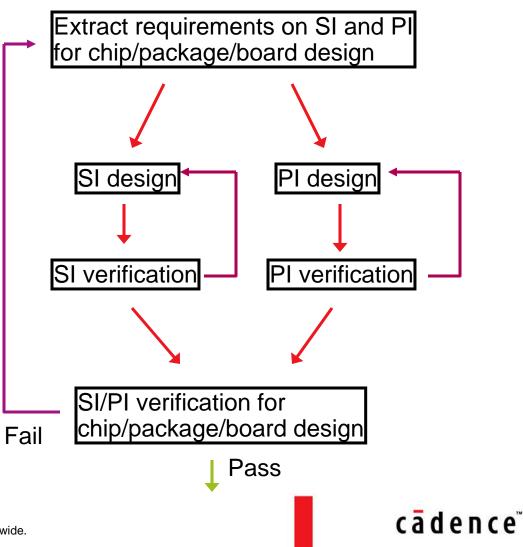

- A general flow for co-design

- Not only to include silicon/package/ board codesign, but also SI and PI codesign and cosimulation

### Problem 1 - Signal analysis: stackup design

#### • Crossection details

|    | Subclass Name                | Туре                 |           | Material         | 3       | Thickness  | Conductivity | Dielectric | Loss<br>Tangent | Negative     | Shield | Width<br>(UM)         | mpedance |

|----|------------------------------|----------------------|-----------|------------------|---------|------------|--------------|------------|-----------------|--------------|--------|-----------------------|----------|

| T  |                              | SURFACE              |           | AIR              |         |            |              |            |                 |              |        |                       |          |

| 2  | WBOND_TOP_STK                | DIESTACK             | -         |                  | _       |            |              |            |                 | s            |        |                       | 1        |

| }  | SPACER1                      | DIELECTRIC           | -         |                  |         |            |              |            |                 |              |        |                       |          |

|    | WBOND_BOT_STK                | DIESTACK             | -         |                  |         |            | 8            |            | 5               | 8 <u>.</u> 3 |        |                       |          |

| 1  | SPACER2                      | DIELECTRIC           | -         |                  |         |            |              |            |                 |              | 8      |                       |          |

| 5  | TOP_COND                     | CONDUCTOR            | *         | COPPER           |         | 30.48      | 595900       | 1.000000   | 0               |              |        | 50.00                 |          |

|    | 1                            | DIELECTRIC           | -         | FR-4             | -       | 60         | 0            | 4.500000   | 0.035           |              | -      |                       |          |

|    | METAL2                       | CONDUCTOR            | *         | COPPER           |         | 30.48      | 595900       | 1.000000   | 0.021           |              |        | 50.00                 |          |

|    |                              | DIELECTRIC           | +         | FR-4             | -       | 125        | 0            | 4.500000   | 0.035           |              |        |                       |          |

| )  | VSS                          | PLANE                | +         | COPPER           | -       | 30.48      | 595900       | 1.000000   | 0.021           |              | ×      | 5                     |          |

|    | a a                          | DIELECTRIC           | -         | FR-4             |         | 200        | 0            | 4.500000   | 0.035           |              |        |                       |          |

| 2  | VDD                          | PLANE                | -         | COPPER           | -       | 30.48      | 595900       | 1.000000   | 0.021           |              | ×      | 8                     | 5        |

|    |                              | DIELECTRIC           | -         | FR-4             |         | 125        | 0            | 4.500000   | 0.035           |              |        |                       |          |

|    | METAL3                       | CONDUCTOR            | +         | COPPER           |         | 30.48      | 595900       | 1.000000   | 0.021           |              |        | 75.00                 |          |

| j. | 1                            | DIELECTRIC           | -         | FR-4             |         | 60         | 0            | 4.500000   | 0.035           |              |        |                       |          |

|    | BOT_COND                     | CONDUCTOR            | -         | COPPER           | -       | 30.48      | 595900       | 1.000000   | 0               |              |        | 75.00                 |          |

|    |                              |                      |           |                  |         |            |              |            |                 |              |        |                       | •        |

| Т  | otal Thickness:<br>752.88 UM | Initializ<br>[ Custo | 102022000 | ductive Layer Di | electri | c: Dielect | ric Constant | : Loss     | Tangent:        |              | Differ | ential Mo<br>olve Moo |          |

cādence

14 © 2007 Cadence Design Systems, Inc. All rights reserved worldwide.

#### **Problem 1 - Signal analysis: establishing** constraints File Edit View Add Display Setup Logic Place Route Analyze Reports Tools Help

Early exploration ...... on multiools DRC Help Þ 🎒 🖪 斄 🗾 😂 🕂 1z 🖻 🖉 🗇 die connection W-Since the net to be extracted is on a diffpair not defined by differential(device models, its xnet mate is not extracted last pick: 2389 559 - 2360 840 No Element Found. Cmd: Idle P A 9800.000, -200.000 ter selection poin

© 2007 Cadence Design Systems, Inc. All rights reserved worldwide. 15

lacksquare

cādence

Find \

### **Problem 1 - Signal analysis: establishing** constraints

© 2007 Cadence Design Systems, Inc. All rights reserved worldwide. 16

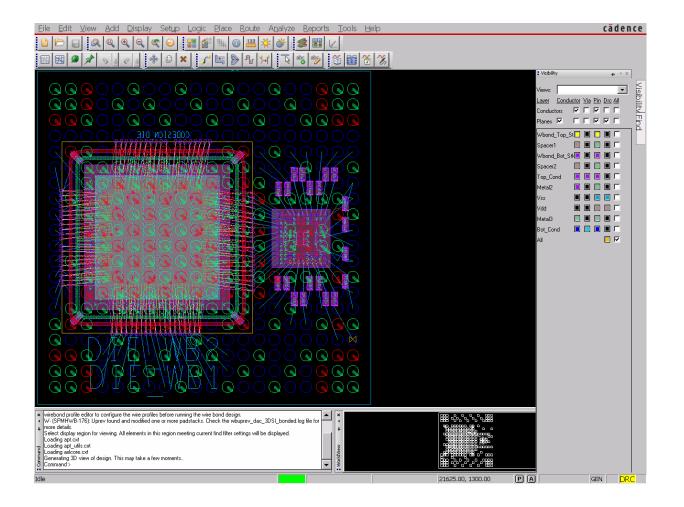

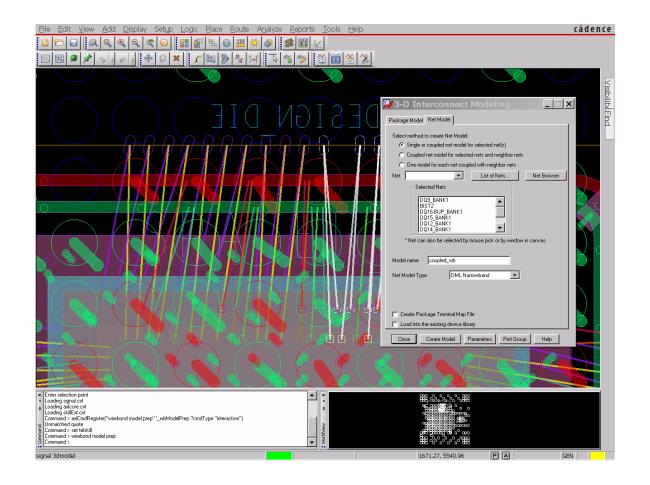

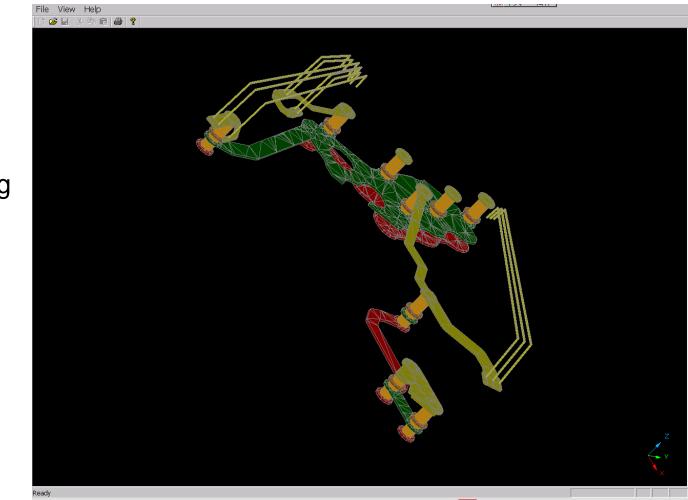

## Problem 1 - Signal analysis: interconnect modeling

- Detailed interconnect modeling

- Wirebonds

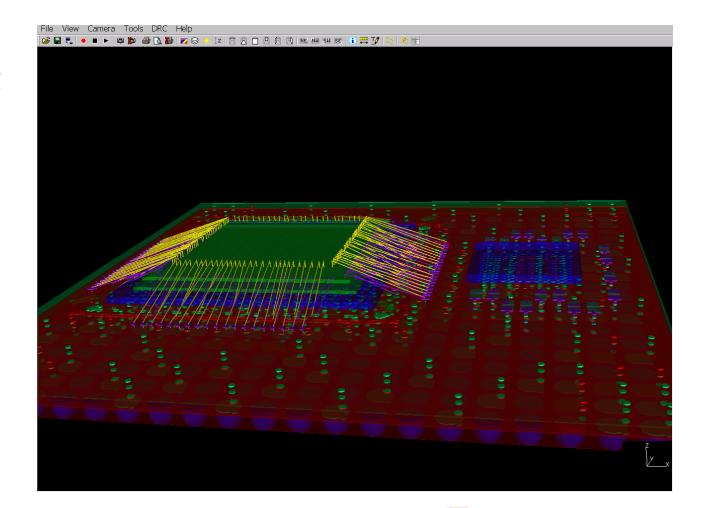

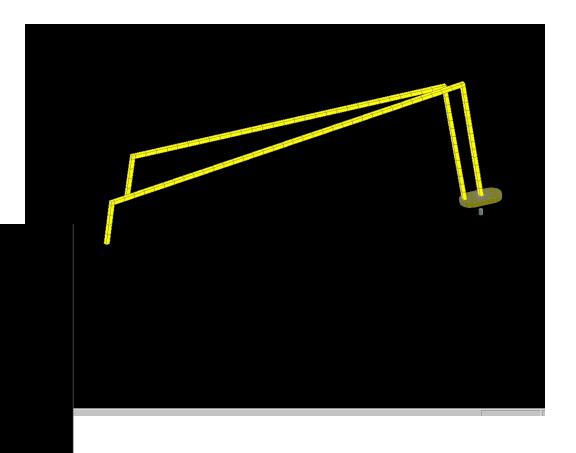

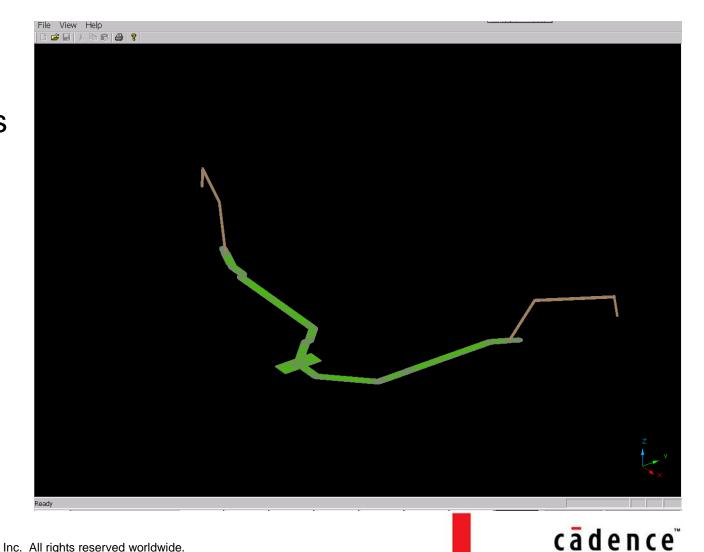

## Problem 1 - Signal analysis: assistant to analysis

- Detailed interconnect modeling

- 3D view

### cādence<sup>~</sup>

### Problem 1 - Signal analysis: wirebond constraints

- Perform what/if analysis by changing wirebond profiles

- Work with existing design and/or start new design

- Edit the parameters

- Update (or extract) constraints

| ctive Profile: PROFI     | LE1         | <b>•</b>       | Add C        | бору | Delete       |        |

|--------------------------|-------------|----------------|--------------|------|--------------|--------|

| laster Definitions:      |             |                |              |      | Load 9       | àave   |

| efinition                |             |                |              |      |              |        |

| irection: Forward Bond   | Material: G | DLD 💌          | Diameter: 10 | JM   | Refresh from | Master |

|                          | Start       |                | 1            | 1    | End          | 1      |

| Horizontal               | Lengt       | h              |              | · ·  |              |        |

| Value 🔤 🚥                | 100 U       | 3.02           |              |      |              |        |

| Vertical                 | Perce       |                |              | •    |              |        |

| Value                    | 50.00       | 0%             |              |      |              |        |

| •                        |             |                |              |      |              |        |

| kample                   |             |                |              |      |              |        |

| ample Start Height: 200  |             | Sample Length: | 2000 UM      |      |              |        |

| ample start height. [200 | - SM        | Sample Lengui. | 12000 011    |      |              |        |

|                          | <u></u>     |                |              |      |              |        |

|                          |             | <u> 100</u> 0  |              |      |              |        |

|                          |             |                |              |      |              |        |

|                          |             | 10000          |              |      |              |        |

|                          |             |                |              |      |              |        |

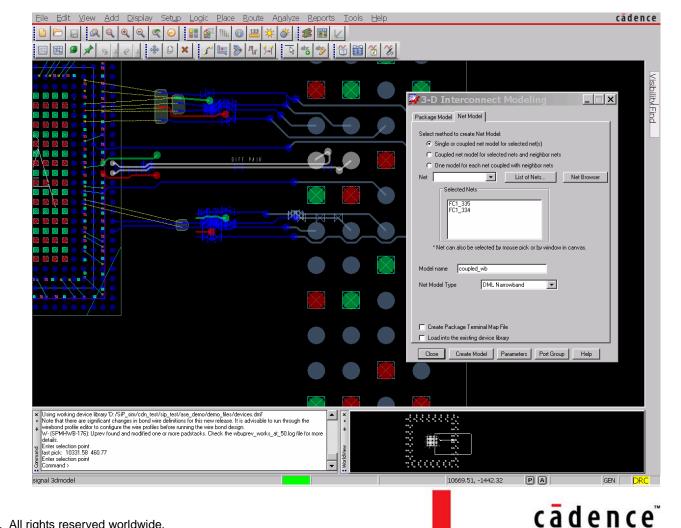

## Problem 1 - Signal analysis: coupled wirebond modeling

Create 3D models of multi-coupled wiorebonds

### cādence<sup>™</sup>

### Problem 1 - Signal analysis: coupled wirebond modeling (cont')

Interested wirebonds

cādence<sup>~</sup>

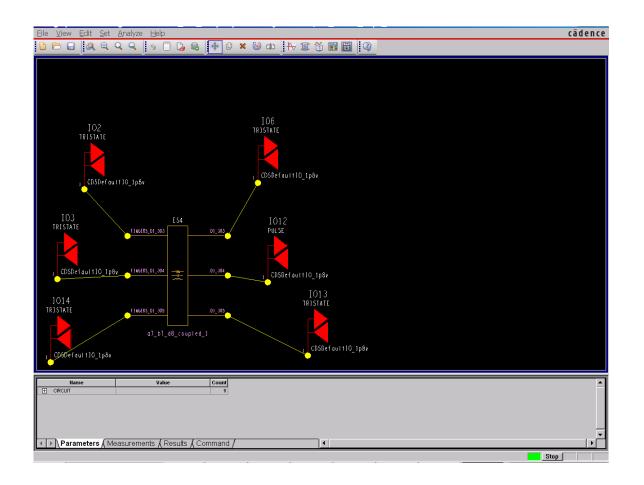

## Problem 1 - Signal analysis: coupled wirebond modeling (cont')

Model validation with topology simulation

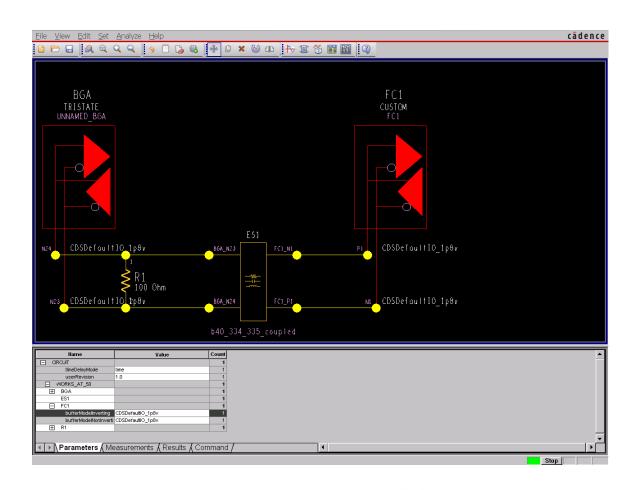

### Problem 1 - Signal analysis: reflections, crosstalks, timing

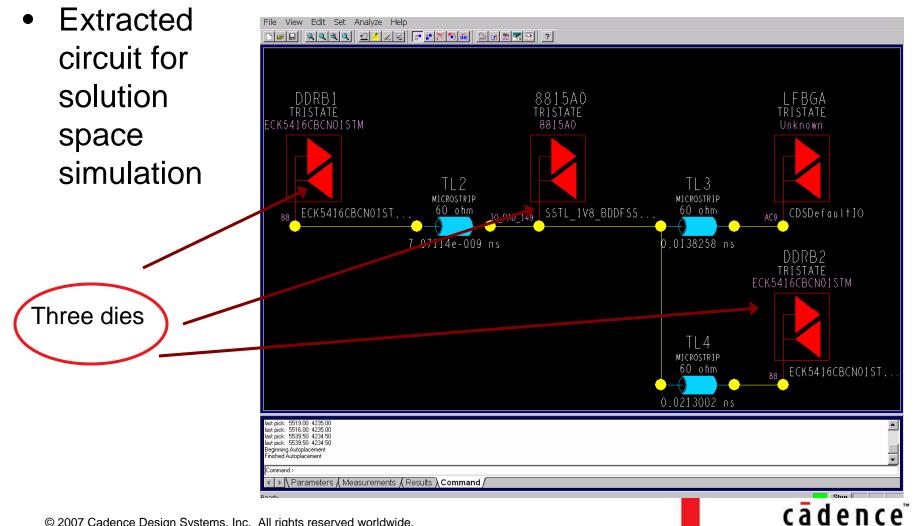

- Building simulation circuits

- Simulating routed nets

- Using 3D models

23 © 2007 Cadence Design Systems, Inc. All rights reserved worldwide.

## Problem 1 - Signal analysis: reflections, crosstalks, timing (cont')

• Simulation circuit

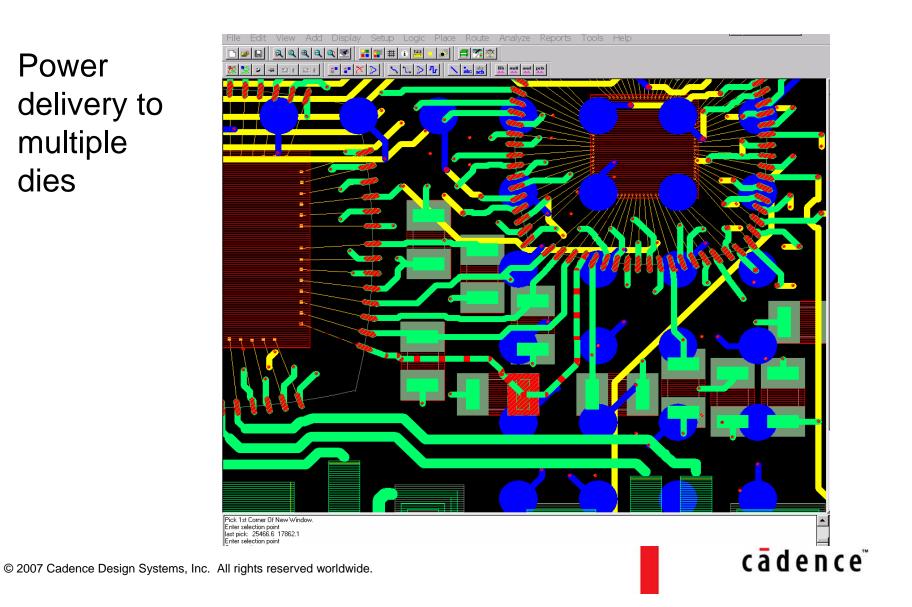

## Problem 2 - Power analysis: power delivery on SiP

• Power delivered to multiple chips through substrate

### **Problem 2 - Power analysis: power delivery**

Power delivery to multiple dies

### Problem 2 - Power analysis: power delivery

Power delivery to multiple dies

### Problem 2 - Power analysis: power delivery

- Power delivery to multiple dies

- Decoupling capacitor selection and placement

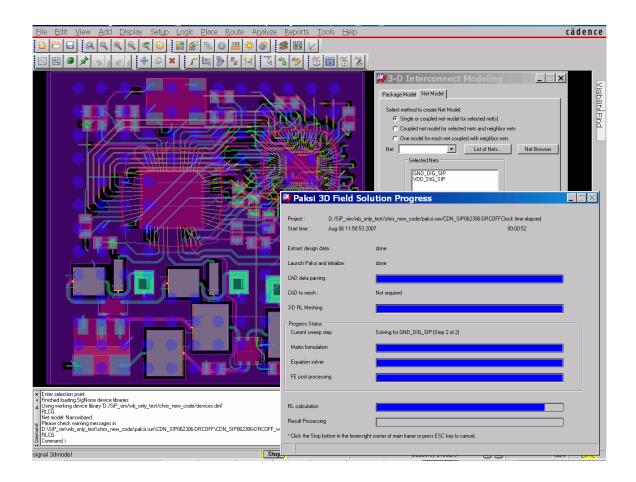

### Problem 2 - Power analysis: decoupling analysis on SiP

- Select power and ground nets that deliver power to multiple dies

- Create coupled 3D models of power/ground nets

- Performa frequency domain analysis on the extracted power/ground model

- Place decoupling capacitors at die pins or at BGA pins, if needed

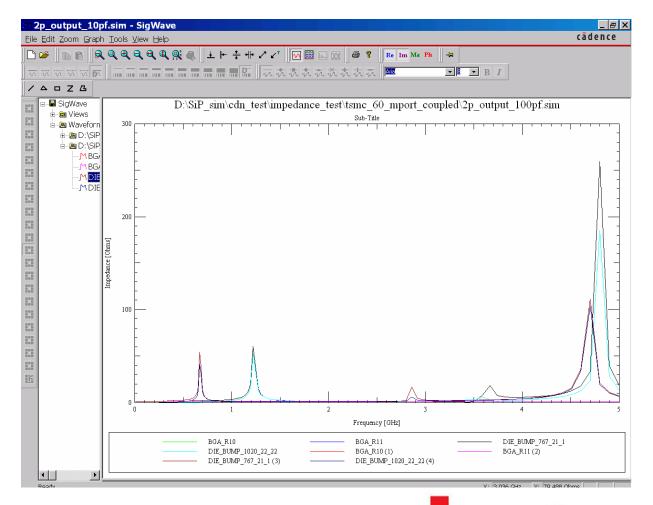

### Problem 2 - Power analysis: decoupling analysis on SiP (cont')

This is the impedance profile at different pin locations

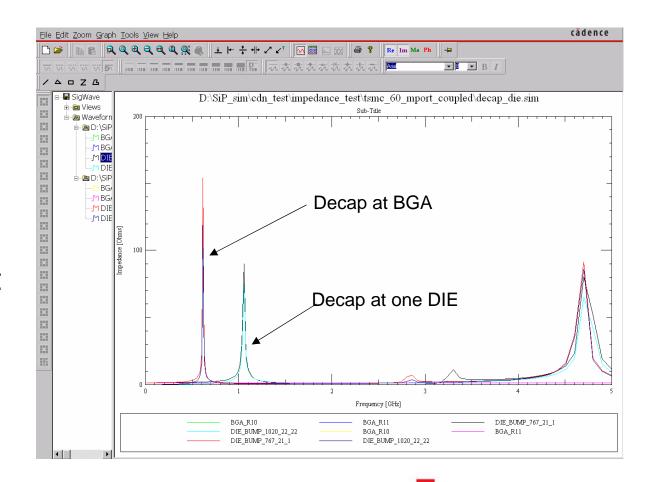

### Problem 2 - Power analysis: decoupling analysis on SiP (cont')

Observe the difference in impedance profile when placing decoupling capacitor at BGA side or at die side

#### 31 © 2007 Cadence Design Systems, Inc. All rights reserved worldwide.

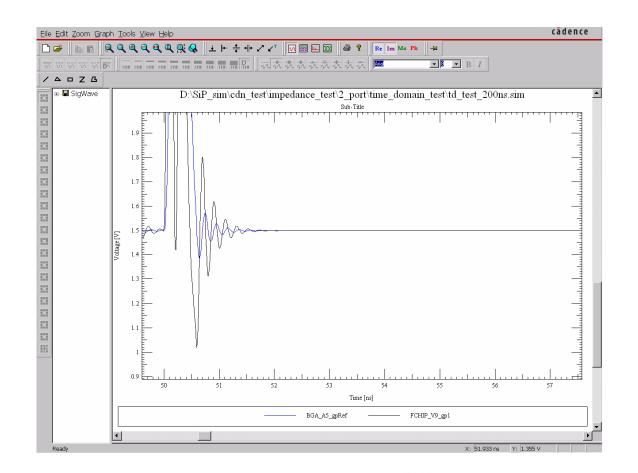

### Problem 2 - Power analysis: time domain simulation on SiP

- Observe time domain waveforms at BGAs and die pins

- This is voltage drop across package in time domain

- Change capacitance values to verify decoupling capacitor effects

### Problem 2 - Power analysis: DC resistance extraction on SiP

- When frequency is set to zero, DC resistance can be obtained

- Using port grouping function, the resistance between any two pins on any net can be extracted

- Then, current drop of the entire path on a DC net can be easily derived

|    | A         | В          | С         | D           | E          | F           | G        | Н |

|----|-----------|------------|-----------|-------------|------------|-------------|----------|---|

| 1  | Parasitic | Extraction | Results   | - (performe | d on Augus | t 06. 2007) | Net Name |   |

| 2  |           |            |           |             |            |             |          |   |

| 3  | Neti      | NetJ       | Rij (mOhm | Lij (nH)    | Cij (pF)   | Gij (uMho)  | Td (ns)  |   |

| 4  | PLL_VDD   | PLL_VDD    | 3.45E+01  | 2.43E+00    | 2.32E+00   | 0           | 7.52E-02 |   |

| 5  | PLL VDD   | NET0365<   | 0.00E+00  | 2.14E-02    | 1.15E-02   | 0           |          |   |

| 6  | NET0365<  | PLL_VDD    | 0.00E+00  | 2.14E-02    | 1.15E-02   | 0           |          |   |

| 7  | PLL_VDD_  | NET0365<   | 0.00E+00  | 1.85E-02    | 1.15E-02   | 0           |          |   |

| 8  | NET0365<  | PLL_VDD_   | 0.00E+00  | 1.85E-02    | 1.15E-02   | 0           |          |   |

| 9  | PLL_VDD   | NET0204    | 0.00E+00  | 3.37E-02    | 2.97E-01   | 0           |          |   |

| 10 | NET0204   | PLL_VDD_   | 0.00E+00  | 3.37E-02    | 2.97E-01   | 0           |          |   |

| 11 | PLL_VDD_  | RESET      | 0.00E+00  | 1.93E-04    | 6.55E-02   | 0           |          |   |

| 12 | RESET     | PLL_VDD    | 0.00E+00  | 1.93E-04    | 6.55E-02   | 0           |          |   |

| 13 | PLL_VDD   | POL        | 0.00E+00  | 5.46E-03    | 3.05E-02   | 0           |          |   |

| 14 | POL       | PLL_VDD_   | 0.00E+00  | 5.46E-03    | 3.05E-02   | 0           |          |   |

| 15 | PLL_VDD   | NET294     | 0.00E+00  | 2.75E-04    | 1.09E-01   | 0           |          |   |

| 16 | NET294    | PLL_VDD    | 0.00E+00  | 2.75E-04    | 1.09E-01   | 0           |          |   |

| 17 | PLL_VDD_  | NET284     | 0.00E+00  | -9.27E-05   | 1.17E-02   | 0           |          |   |

| 18 | NET284    | PLL_VDD    | 0.00E+00  | -9.27E-05   | 1.17E-02   | 0           |          |   |

| 19 | PLL_VDD   |            |           | -1.35E-03   |            | 0           |          |   |

| 20 | NET251    | PLL VDD    | 0.00E+00  | -1.35E-03   | 1.17E-02   | 0           |          |   |

| 21 | PLL VDD   |            |           | -1.61E-03   |            | 0           |          |   |

| 22 | NET249    | PLL VDD    | 0.00E+00  | -1.61E-03   | 1.07E-02   | 0           |          |   |

| 23 | PLL VDD   | F 44MHZ    | 0.00E+00  | -2.68E-03   | 2.34E-02   | 0           | 1        |   |

| 24 | F 44MHZ   | PLL VDD    | 0.00E+00  | -2.68E-03   | 2.34E-02   | 0           |          |   |

| 25 | PLL VDD   | CHS<3>     | 0.00E+00  | -1.53E-03   | 2.32E-02   | 0           |          |   |

| 26 | CHS<3>    | PLL VDD    | 0.00E+00  | -1.53E-03   | 2.32E-02   | 0           |          |   |

| 27 | PLL_VDD   | CHS<2>     | 0.00E+00  | -1.86E-03   | 2.33E-02   | 0           |          |   |

| 28 | CHS<2>    | PLL_VDD    | 0.00E+00  | -1.86E-03   | 2.33E-02   | 0           |          |   |

| 29 | NET0365<  | NET0365<   | 5.99E+02  | 1.03E+01    | 1.97E+00   | 0           | 1.43E-01 |   |

| 30 | NET0365<  | NET0365<   | 0.00E+00  | 4.47E-01    | 6.78E-02   | 0           |          |   |

| 31 | NET0365<  | NET0365<   | 0.00E+00  | 4.47E-01    | 6.78E-02   | 0           |          |   |

| 32 | NET0365<  | NET0204    | 0.00E+00  | 3.03E-02    | 1.20E-02   | 0           |          |   |

| 33 | NET0204   | NET0365<   | 0.00E+00  | 3.03E-02    | 1.20E-02   | 0           |          |   |

| 34 | NET0365<  | RESET      | 0.00E+00  | -6.56E-02   | 2.43E-02   | 0           |          |   |

| 35 | RESET     | NET0365<   | 0.00E+00  | -6.56E-02   | 2.43E-02   | 0           |          |   |

| 36 | NET0365<  |            |           | 1.25E-01    |            | 0           |          |   |

|    | POL       |            | 0.00E+00  |             | 2.43E-02   | 0           |          |   |

| 38 | NET0365<  |            | 0 00E+00  |             |            | n           |          |   |

cādence

33 © 2007 Cadence Design Systems, Inc. All rights reserved worldwide.

- System-in-Package is the right integration solution for wireless and consumer products

- It posts great challenges to designs and analyses (differences between single package and PCB designs)

- IC-Package-Board co-design and co-simulation methodologies are key to successful SiP designs

- Cadence provides a design and analysis environment to meet digital SiP design requirements

- SI and PI solutions need to support multiple die designs

- Interconnect designs, stacked die configurations, etc...

- SI and PI solutions are implemented in Cadence's Digital SiP environment

### CONNECT: IDEAS

cādence™

### **CDNLive! 2007 Silicon Valley**