# **Encounter Diagnostics**

A single, unified engine for both precision and volume diagnostics

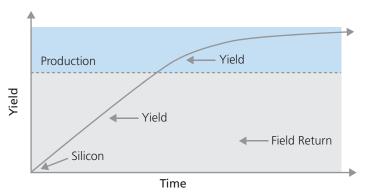

Yield loss is one of the most significant challenges in sub-90nm processes. Traditional in-line inspection techniques no longer keep pace with increasing defect types caused by subtle design process variations. Cadence® Encounter® Diagnostics is the industry's most advanced solution for accelerating yield ramp and reducing costs in manufacturing environments. It rapidly analyzes thousands of failures, identifies the source of systematic yield loss, and pinpoints defect location in the netlist and layout.

# **Encounter Diagnostics**

Part of the Encounter Test family, Encounter Diagnostics offers a comprehensive solution for silicon bring-up and debug with advanced fault modeling to boost productivity and predictability, reduce development costs, and accelerate time to market. It offers an industry-leading 80-100% defect identification rate as verified by physical failure analysis.

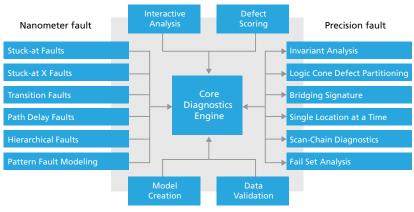

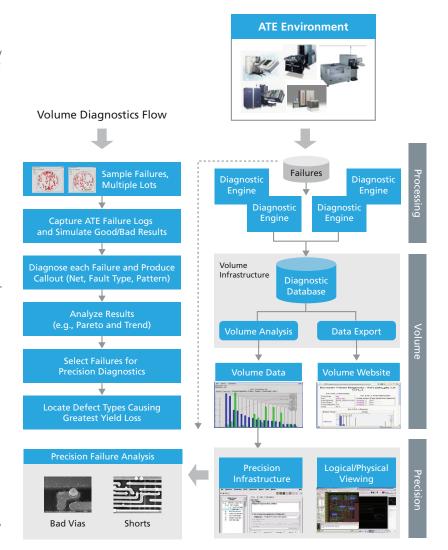

Encounter Diagnostics supports volume and precision operating modes, static and dynamic diagnostics, patented pattern fault modeling, schematic cross-probing between logic and physical models, and all industry-standard automated test pattern generation (ATPG) test vector formats.

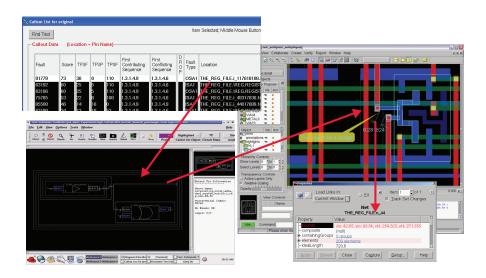

In volume mode, Encounter Diagnostics uses advanced statistical analysis with an SQL-compatible database to analyze diagnostic callouts, and it uses failure data to identify the primary yield-limiting issues. Volume analysis supports both logic and physical attributes. In precision mode, it pinpoints nanometer defects using capabilities such as scan-chain diagnostics, advanced callout analysis, diagnostics

### Comprehensive Decision Analysis

Universal ATPG/ATE flow support

Figure 1: Encounter Diagnostics offers a unified system with a single-core engine for volume and precision diagnostics, bringing higher productivity and predictability to the ATPG and diagnostic flows

test pattern generation, invariant analysis, and an advanced integrated GUI analysis environment that supports schematic cross-probing between logic and physical models.

# Encounter Diagnostics is available in two offerings:

Encounter Diagnostics L (Basic) for precision-based bring-up applications  Encounter Diagnostics XL (Volume and Precision Diagnostics Engine Pack), which offers four diagnostics engines and adds volume analysis and enhanced navigation capabilities

### **Benefits**

- Uses a single, unified engine for precision and volume diagnostics

- Identifies the most critical yield-limiting design process issues

- Locates root cause defects with 80% or greater accuracy

- Isolates faults efficiently with bi-directional cross-probing between logic and physical models

- Enables physical design browsing to extract physical attributes and further localize yield limiters

- X-Y-Z location reporting of suspected defects maximizes the effectiveness of physical failure analysis lab equipment

- Analyzes thousands of failed devices quickly

- Universal ATPG vector support enables easy integration with any flow

- Patented pattern fault modeling optimizes 65nm, 45nm, and 32nm defect identification

- Increases the value of your existing automated yield learning system

- Offers a scalable solution that uses multiple processors or servers and a robust SQL-compatible database

- Offers a complete tool kit of algorithms and heuristics for detecting the most challenging design process defects

- Identifies scan-chain defects

- Locates failures in customer field returns

### **Encounter Test**

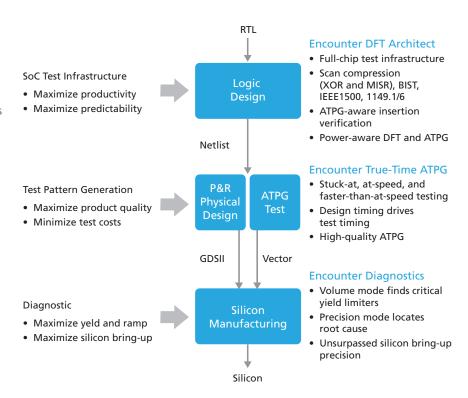

Part of the Encounter digital design and implementation platform, the Encounter Test product family delivers an advanced silicon verification and yield learning system. Encounter Test comprises three product technologies:

• Encounter DFT Architect: ensures ease of use, productivity, and predictability in generating ATPG-ready netlists containing DFT structures, from the most basic to the most complex; available as an add-on option to Encounter RTL Compiler

Figure 2: Encounter Diagnostics significantly improves productivity and timeframes for silicon debug, yield ramp, yield learning, and field return analysis

- Encounter True-Time ATPG: ensures the fewest test escapes and the highest quality shipped silicon at the lowest development and production costs

- Encounter Diagnostics: delivers the most accurate volume and precision diagnostics capabilities to accelerate yield ramp and optimize device and fault modeling

Encounter Test also offers a flexible API using the PERL language to retrieve design data from its pervasive database. This unique capability allows you to customize reporting, trace connections in the design, and obtain information that might be helpful for debugging design issues or diagnostics.

Figure 3: Encounter Test offers a complete RTL-to-silicon verification flow and methodologies that enable the highest quality IC devices at the lowest cost

www.cadence.com 2

### **Features**

### Encounter Diagnostics L (Basic)

Diagnostics L provides a precision-only diagnostics product. It precisely locates the root-cause defects in a given silicon die, which is critical for initial silicon debug, yield learning, and field failure analysis. Diagnostics L can achieve 80% or greater accuracy through features including scan-chain diagnostics, transition diagnostics, and multi-defect fault identification, which helps identify the presence of multiple defects.

Scan-chain diagnostics uses special algorithms to identify problems within the scan chains themselves. Transition diagnostics identifies faults that cause delay test failures. Logic-cone defect partitioning helps separate faults in ICs that have multiple defects. Pattern fault modeling allows you to define powerful customized fault models to target virtually any logical or physical (bridging) defect. If the existing test vectors cannot produce a discernable isolated fault, Diagnostics L can create additional test vectors that will target each potential fault independently and run in an optimized fashion on probing equipment.

# Encounter Diagnostics XL (Volume and Precision Diagnostics Engine Pack)

Diagnostics XL offers both volume and precision diagnostics capability via its engine pack (four diagnostics engines). In precision mode, it provides all the capabilities of the Basic product, including applications for yield ramp and yield learning. Volume diagnostics, however, is a rapidly emerging application for systematically identifying the most critical systemic yield issues that impact manufacturing profit and supply-demand challenges. Diagnostics XL adds volume analysis capabilities through the multi-engine pack to deliver a comprehensive volume diagnostics flow.

Diagnostics XL uniquely supports volume diagnostics with a number of advanced features including a fully SQL-compatible database, fail set analysis, parallel runtime support, failsafe termination, automated fault selection, and a data extraction programming interface.

Figure 4: Physically-aware precision diagnostics enables fault cross-probing from callout to logic schematic to X-Y-Z location in the physical design

Figure 5: In the Diagnostic XL environment, a volume diagnostics flow drives productive and predictable precision diagnostics and precision failure analysis (PFA)

www.cadence.com 3

Parallel runtime support enables simultaneous execution across multiple processors or servers to maximize throughput. Volume diagnostics can run in standalone batch mode (wherein you select the fail sets to analyze) or can be integrated as a subsystem in an automated yield learning environment.

In the latter case, the main points of integration are automatic fail-set selection and automatic results analysis using the data extraction interface.

Diagnostics XL has been enhanced with a full-function, highly efficient physical layout browsing capability to quickly identify physical structures causing failures. The layout browser integrates with existing Encounter Diagnostics analysis capabilities. This enables bi-directional cross-probing between the logical schematic viewer and the physical layout browser, and uni-directional cross-probing from the view callout list function to the layout browser when localizing a failure. The layout browser reads layout information stored in an OpenAccess database (version 2.2 or higher). The Cadence Virtuoso® physical layout browser is also supported for cross-probing.

A web-based journaling capability ensures cross-organizational access to critical information that can be customized for specific interests and purposes.

Encounter Test offers a flexible API using the PERL language to retrieve design data from its pervasive database. This unique capability allows users to customize reporting, trace connections in the design, and obtain information that might be helpful for debugging design issues or diagnostics.

# Failures Diagnostic Runs

### Volume Website

- Automated Creation

- Customizable Outputs

Figure 6: Web-based volume diagnostics reporting

### **Platforms**

- Sun Solaris (64-bit)

- Linux (32-bit, 64-bit)

- IBM AIX (64-bit)

## **Cadence Services and Support**

- Cadence application engineers can answer your technical questions by telephone, email, or Internet—they can also provide technical assistance and custom training

- Cadence certified instructors teach more than 70 courses and bring their real-world experience into the classroom

- More than 25 Internet Learning Series (iLS) online courses allow you the flexibility of training at your own computer via the Internet

- Cadence Online Support gives you 24x7 online access to a knowledgebase of the latest solutions, technical documentation, software downloads, and more

Cadence is transforming the global electronics industry through a vision called EDA360. With an application-driven approach to design, our software, hardware, IP, and services help customers realize silicon, SoCs, and complete systems efficiently and profitably. <a href="https://www.cadence.com">www.cadence.com</a>